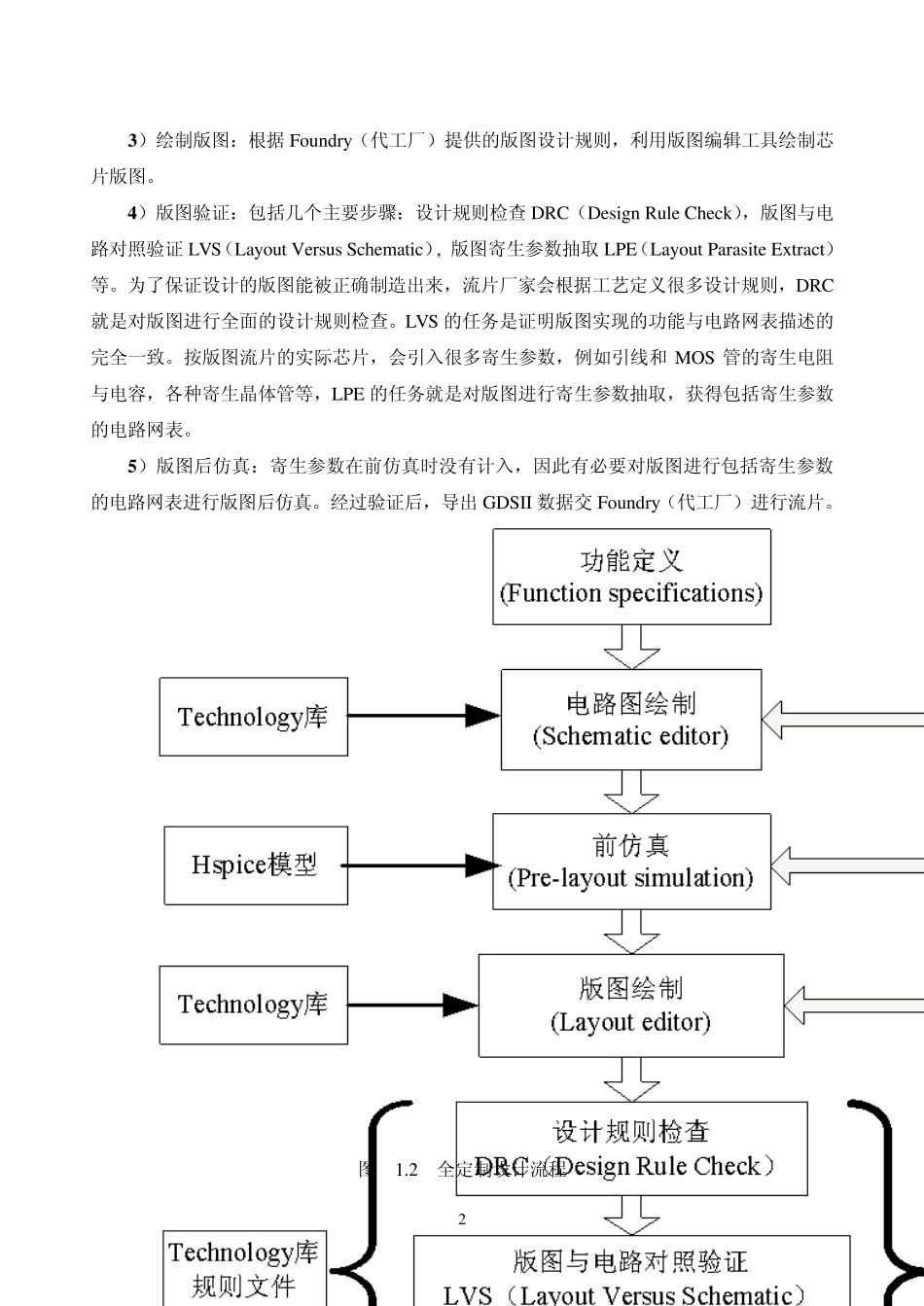

1 第一章 IC 设计的基本知识 集成电路设计方法大致可分为定制(Cu stom)、半定制(Semi-cu stom)、可编程逻辑器件(PLD)等设计方法,如图 1.1 所示。定制设计方法又可分为全定制(Fu ll-Cu stom)设计和基于包(Celll-Based)的设计方法二类。本课程讲授集成电路定制设计方法。半定制和可编程逻辑器件安排在其它课程中。 定制(C ustom )全 定制(F ull-C ustum )半 定制(Sem i-C ustum )可编 程 逻 辑 器 件(P L D )A SIC 设计基 于 包(C ell-B ased)线 性 陈 列(L inear A rrays)门 陈 列(G ate A rrays)F P G AC P L D 图 1.1 ASIC设计方法分类 1.1 集成电路设计流程 全定制(Fu ll-Cu stom)设计和基于包(Celll-Based)的设计方法使用不同的设计流程,所使用的设计工具也会有所不同。 1.1.1 全定制设计流程 全定制(fu ll cu stom)集成电路设计方法,是按规定的功能与性能要求,对电路的结构布局与布线进行最优化设计,实现最小面积,最佳布线布局、最优功耗速度积,以求获得尽可能最优的设计。全定制(fu ll cu stom)集成电路设计方法通常用于高性能的设计场合:规模较小性能要求较高的中小规模专用集成电路;大批量高性能集成电路,例如 CPU 与内存;需要最佳优化设计的标准单元库等等。图 1.2 是全定制设计流程,大致的步骤如下: 1)电路图绘制:根据芯片的功能要求与性能指标,选择合适的集成电路工艺库,使用电路图编辑工具绘制电路图。 2)前仿真:利用 HSPICE 对电路图进行仿真(版图前仿真),并进行性能优化。 2 3 )绘制版图:根据Fou ndry (代工厂)提供的版图设计规则,利用版图编辑工具绘制芯片版图。 4 )版图验证:包括几个主要步骤:设计规则检查 DRC(Design Ru le Check),版图与电路对照验证 LVS(Lay ou t Versu s Schematic), 版图寄生参数抽取 LPE(Lay ou t Parasite Ex tract)等。为了保证设计的版图能被正确制造出来,流片厂家会根据工艺定义很多设计规则,DRC就是对版图进行全面的设计规则检查。LVS 的任务是证明版图实现的功能与电路网表描述的完全一致。按版图流片的实际芯片,会引入很多寄生参数,例如引线和 MOS 管的寄生电阻与电容,各种寄生晶体管等,LPE 的任务就是对版图进行寄生参数抽取,获得包括寄生参数的电路网表。 5 )版图后仿真:寄生参数在前仿真时没有计入...