第1 节 并行输入/输出内核 并行输入/输出(PIO)内核提供了Avalon存储器映射从端口和通用IO端口直接的接口

I/O端口连接到片内的用户逻辑或是连到与 FPGA片外设备相连的引脚上

PIO内核提供对用户逻辑或外部设备简单的I/O访问,应用实例如下: 控制 LED 获取开关数据 控制显示设备 配置并与片外设备通信,例如专用标准产品(ASSP)的设备

PIO内核可以基于输入信号而发出中断请求 (IRQ) 输出

SOPC Builder中提供了现成的 PIO内核,可以很容易地将 PIO内核集成到 SOPC Builder生成的系统中

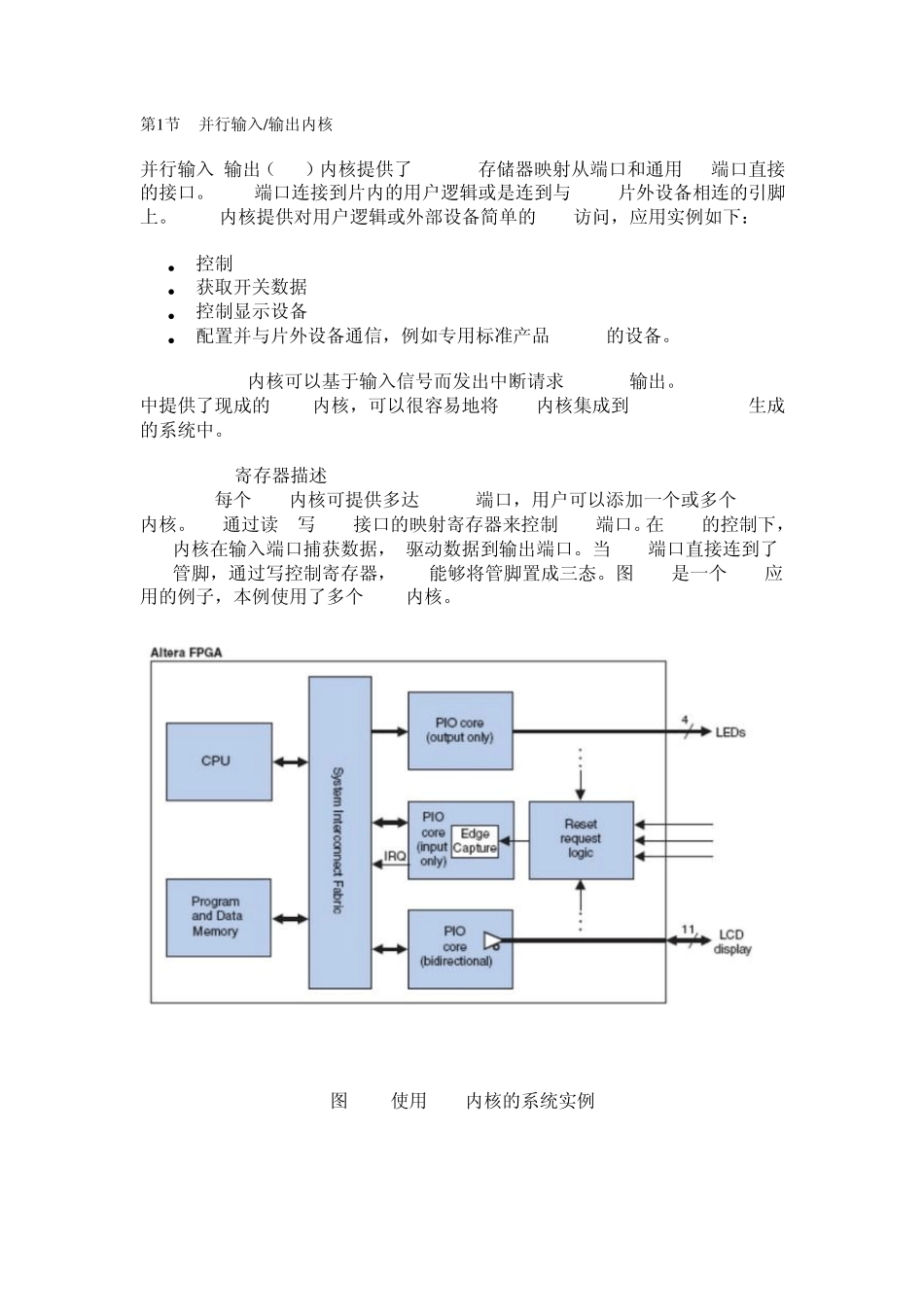

1 PIO 寄存器描述 每个 PIO内核可提供多达 32I/O端口,用户可以添加一个或多个 PIO内核

CPU通过读/ 写 PIO接口的映射寄存器来控制 PIO端口

在 CPU的控制下,PIO内核在输入端口捕获数据, 驱动数据到输出端口

当 PIO端口直接连到了I/O管脚,通过写控制寄存器,CPU能够将管脚置成三态

图 7-1是一个 PIO应用的例子,本例使用了多个 PIO内核

图 7-1 使用PIO内核的系统实例 当集成到SOPC Builder生成的系统中,PIO内核有两个特性对用户是可见的

具有四个寄存器的存储器映射的寄存器空间,4个寄存器是data、direction、 interruptmask和 edgecapture

1到32个的I/O端口

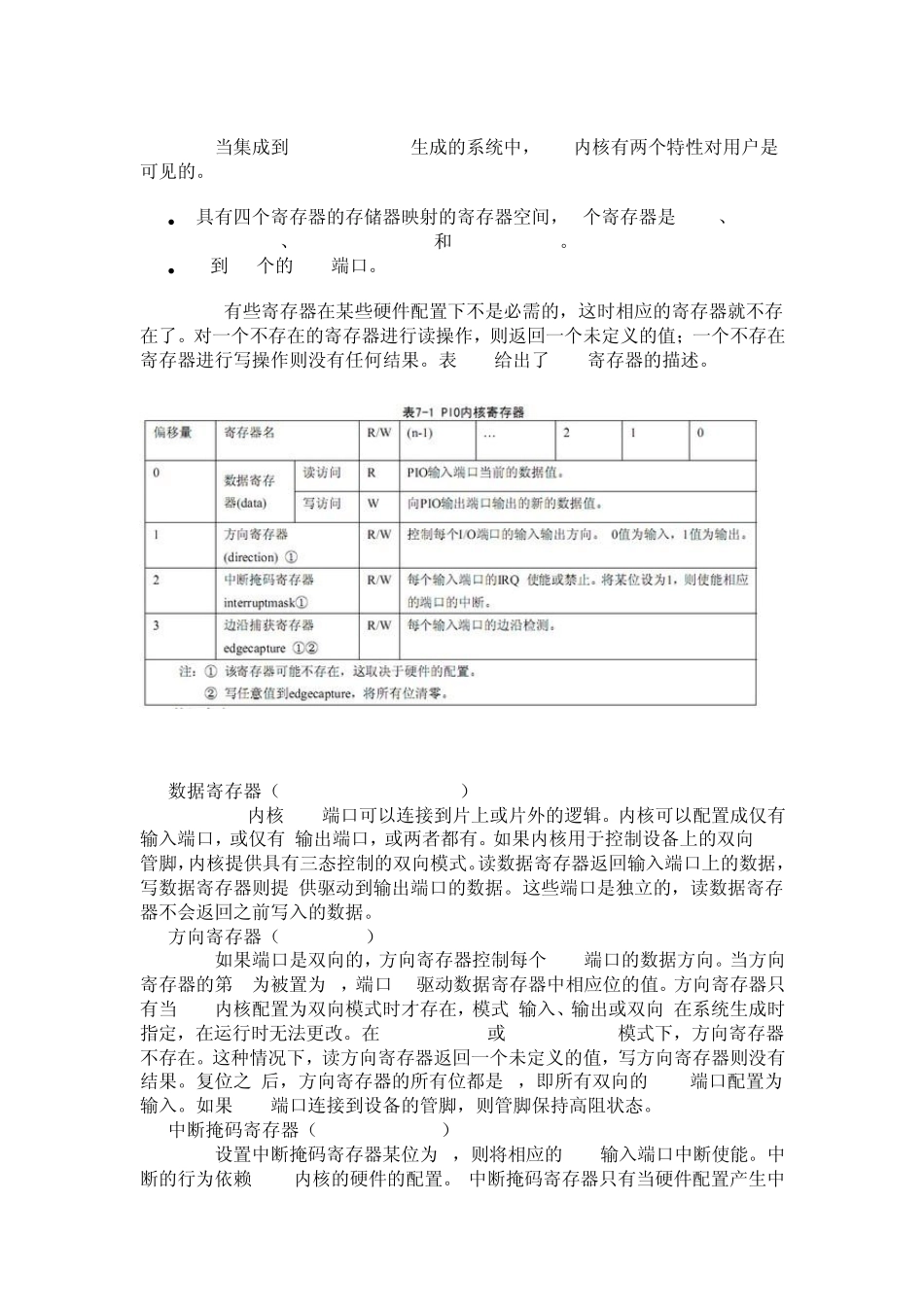

有些寄存器在某些硬件配置下不是必需的,这时相应的寄存器就不存在了

对一个不存在的寄存器进行读操作,则返回一个未定义的值;一个不存在寄存器进行写操作则没有任何结果

表 7-1给出了 PIO寄存器的描述

数据寄存器(Data Input & Output) PIO内核I/O端口可以连接到片上或片外的逻辑

内核可以配置成仅有输入端口,或仅有