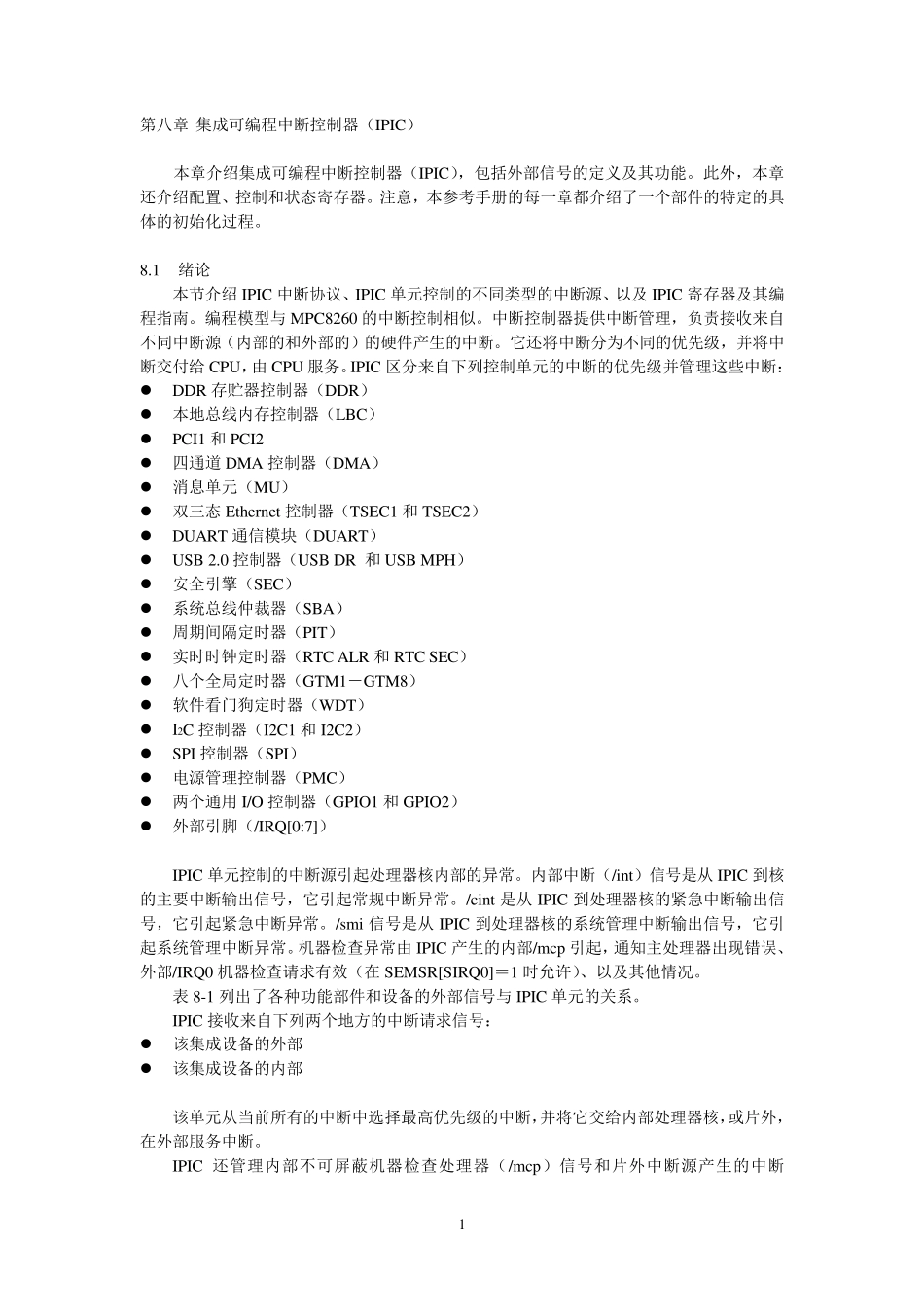

1 第八章 集成可编程中断控制器(IPIC) 本章介绍集成可编程中断控制器(IPIC),包括外部信号的定义及其功能。此外,本章还介绍配置、控制和状态寄存器。注意,本参考手册的每一章都介绍了一个部件的特定的具体的初始化过程。 8.1 绪论 本节介绍IPIC 中断协议、IPIC 单元控制的不同类型的中断源、以及IPIC 寄存器及其编程指南。编程模型与 MPC8260 的中断控制相似。中断控制器提供中断管理,负责接收来自不同中断源(内部的和外部的)的硬件产生的中断。它还将中断分为不同的优先级,并将中断交付给 CPU,由 CPU 服务。IPIC 区分来自下列控制单元的中断的优先级并管理这些中断: DDR 存贮器控制器(DDR) 本地总线内存控制器(LBC) PCI1 和 PCI2 四通道 DMA 控制器(DMA) 消息单元(MU) 双三态 Ethernet控制器(TSEC1 和 TSEC2) DUART 通信模块(DUART) USB 2.0 控制器(USB DR 和 USB MPH) 安全引擎(SEC) 系统总线仲裁器(SBA) 周期间隔定时器(PIT) 实时时钟定时器(RTC ALR 和 RTC SEC) 八个全局定时器(GTM1-GTM8) 软件看门狗定时器(WDT) I2C 控制器(I2C1 和 I2C2) SPI 控制器(SPI) 电源管理控制器(PMC) 两个通用I/O 控制器(GPIO1 和 GPIO2) 外部引脚(/IRQ[0:7]) IPIC 单元控制的中断源引起处理器核内部的异常。内部中断(/int)信号是从IPIC 到核的主 要 中断输 出 信号,它引起常规 中断异常。/cint 是从IPIC 到处理器核的紧 急 中断输 出 信号,它引起紧 急 中断异常。/smi 信号是从IPIC 到处理器核的系统管理中断输 出 信号,它引起系统管理中断异常。机 器检 查 异常由 IPIC 产生的内部/mcp 引起,通知 主 处理器出 现 错 误 、外部/IRQ0 机 器检 查 请 求 有 效 (在 SEMSR[SIRQ0]= 1 时允 许 )、以及其他 情 况 。 表 8-1 列出 了各 种 功能部件和设 备 的外部信号与 IPIC 单元的关 系。 IPIC 接收来自下列两个地方 的中断请 求 信号: 该 集成设 备 的外部 该 集成设 备 的内部 该 单元从当 前 所 有 的中断中选 择 最 高 优先级的中断,并将它交给内部处理器核,或 片 外,在 外部服务中断。 IPIC 还管理内部不可屏 蔽 机 器检 查 处理器(/mcp)信号...