基于 VHDL 的异步串行通信电路设计1 引 言 随着电子技术的开展,现场可编程门阵列 FPGA 和复杂可编程逻辑器件 CPLD 的出现,使得电子系统的设计者利用与器件相应的电子 CAD 软件,在实验室里就可以设计自己的专用集成电路 ASIC 器 件

这种可编程 ASIC 不仅使设计的产品到达小型化、集成化和高可靠性,而且器件具有用户可编程特性,大大缩短了设计周期,减少了设计费用,降低了设计风 险

目前数字系统的设计可以直接面对用户需求,根据系统的行为和功能要求,自上至下地逐层完成相应的描述﹑综合﹑优化﹑仿真与验证,直到生成器件,实现电 子设计自动化

其中电子设计自动化〔EDA〕的关键技术之一就是可以用硬件描述语言〔HDL〕来描述硬件电路

VHDL 是用来描述从抽象到具体级别硬件的工业标准语言,它是由美国国防部在 80 年代开发的 HDL,现在已成为 IEEE 成认的标准硬件描述语言

VHDL 支持硬件的设计、验证、综合和测试,以及硬件设计数据的交换、维护、修改和硬件的实现,具有描述能力强、生命周期长、支持大规模设计的分解和已有设计的再 利用等优点

利用 VHDL 这些优点和先进的 EDA 工具,根据具体的实际要求,我们可以自己来设计串口异步通信电路

广告插播信息维库最新热卖芯片: EL1501CM EL7457CU LT1640ALCS8 LTC1439CG MAX241EEAI AD9203ARUZ QMV72DP5 IRF7459 MAX706CPA PBL3770A 2 串口异步通信的帧格式和波特率 2

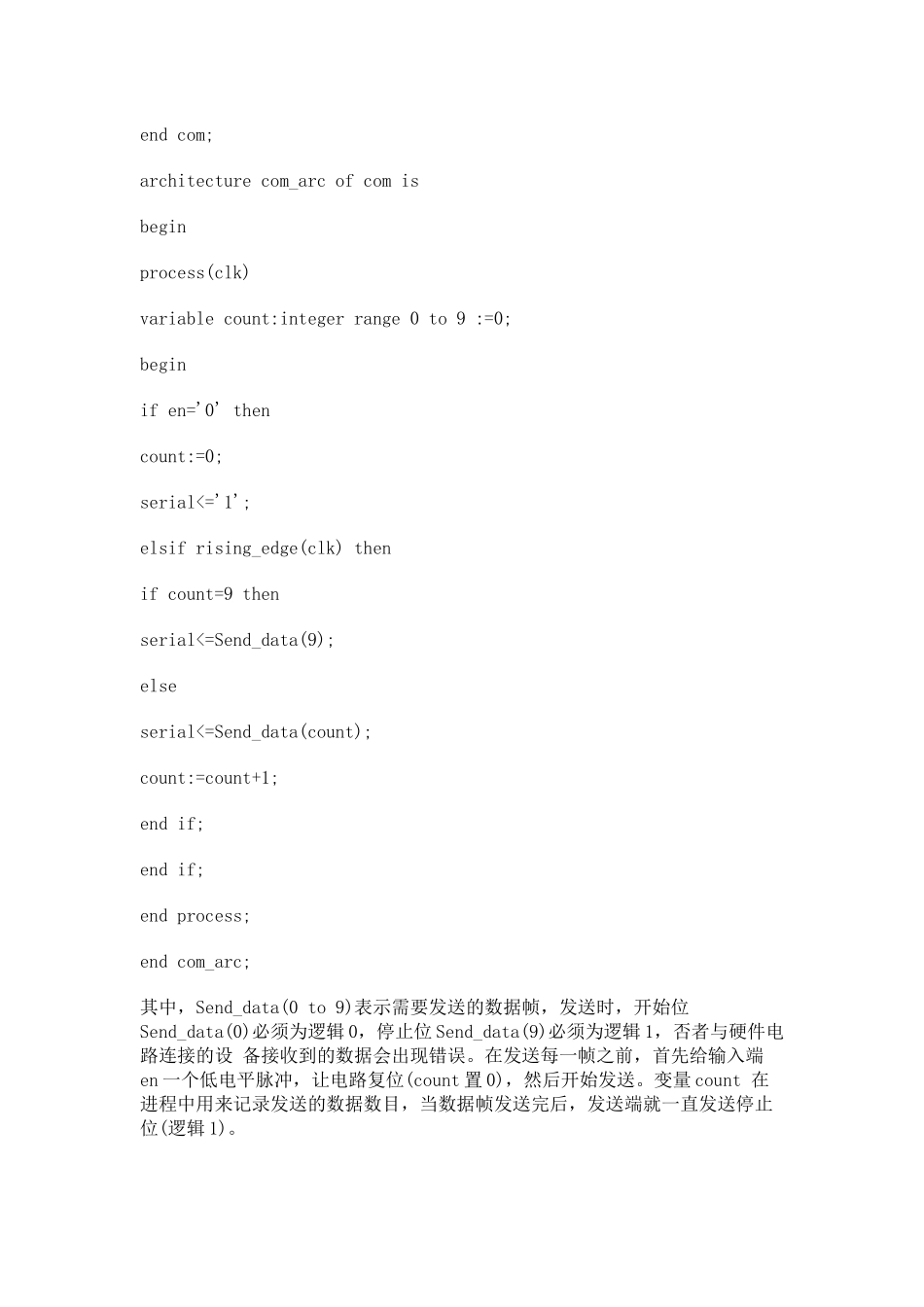

1 串行异步通信的帧格式 在串行异步通信中,数据位是以字符为传送单位,数据位的前、后要有起始位、停止位,另外可以在停止位的前面加上一个比特位(bit)的校验位

其 帧格式如图 1 所示

起始位是一个逻辑 0,总是加在每一帧的开始,为的是提醒数据接收设备接收数据