实验报告实验中心电子信息技术实验教学中心专业年级2024 级电子信息科学与技术实验课程电子电路 CAD姓 名实验名称实验 8 逻辑模拟和数模混合模拟学 号提交日期成 绩一、实验目的1、使学生理解逻辑模拟的涵义;2、使学生掌握逻辑模拟激励信号的设置方法; 3、掌握逻辑模拟和数模混合模拟的方法

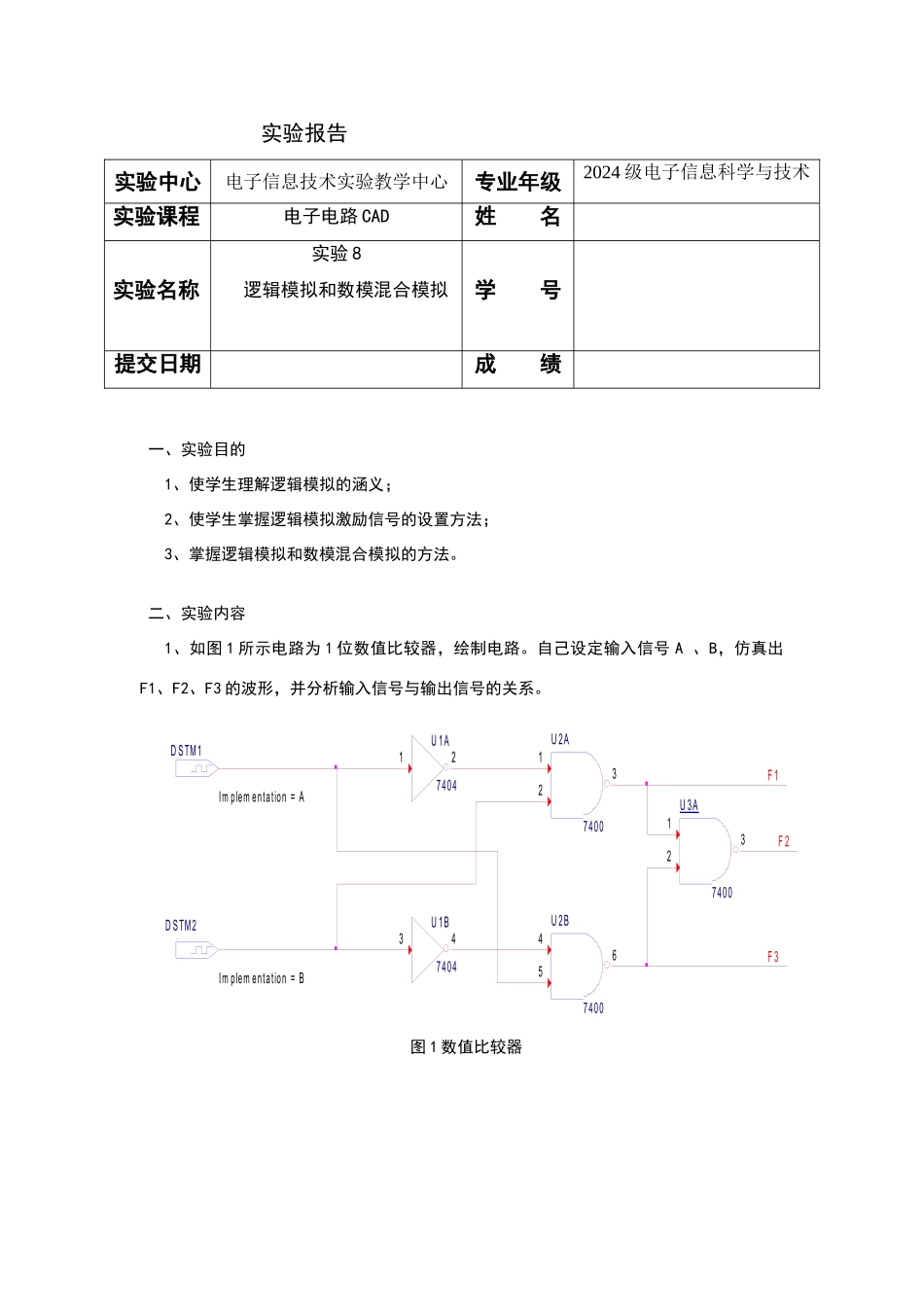

二、实验内容1、如图 1 所示电路为 1 位数值比较器,绘制电路

自己设定输入信号 A 、B,仿真出F1、F2、F3 的波形,并分析输入信号与输出信号的关系

S 1D STM1Im plem entation = AS 1D STM2Im plem entation = BU 1A740412U 1B740434U 2A7400123U 2B7400456U 3A7400123F 1F 2F 3图 1 数值比较器图 2 参数设置图 3 时钟信号参数设置 Time Time0s50us100us150us200us250us300us350us400us450us500us STM1:OUT STM2:OUT F1 F2 F3图 4 输入波形和输出波形2、输入信号与输出信号的关系; ; 图 5真值表S 1D STM1Im plem entation = DS 1D STM2Im plem entation = C LKS 1D STM3Im plem entation = C LRU 1A7474C LK3C LR1D2PR E4Q5Q6U 1B7474C LK11C LR13D12PR E10Q9Q8U 2A7474C LK3C LR1D2PR E4Q5Q6U 2B7474C LK11C LR13D12PR E10Q9Q8H IQ[3:0]Q0Q1Q2Q3图 5 移位寄存器ABF1F2F300101010111011011101图 6 参数设置图 7 时钟信号参数设置输入信号:D,CL