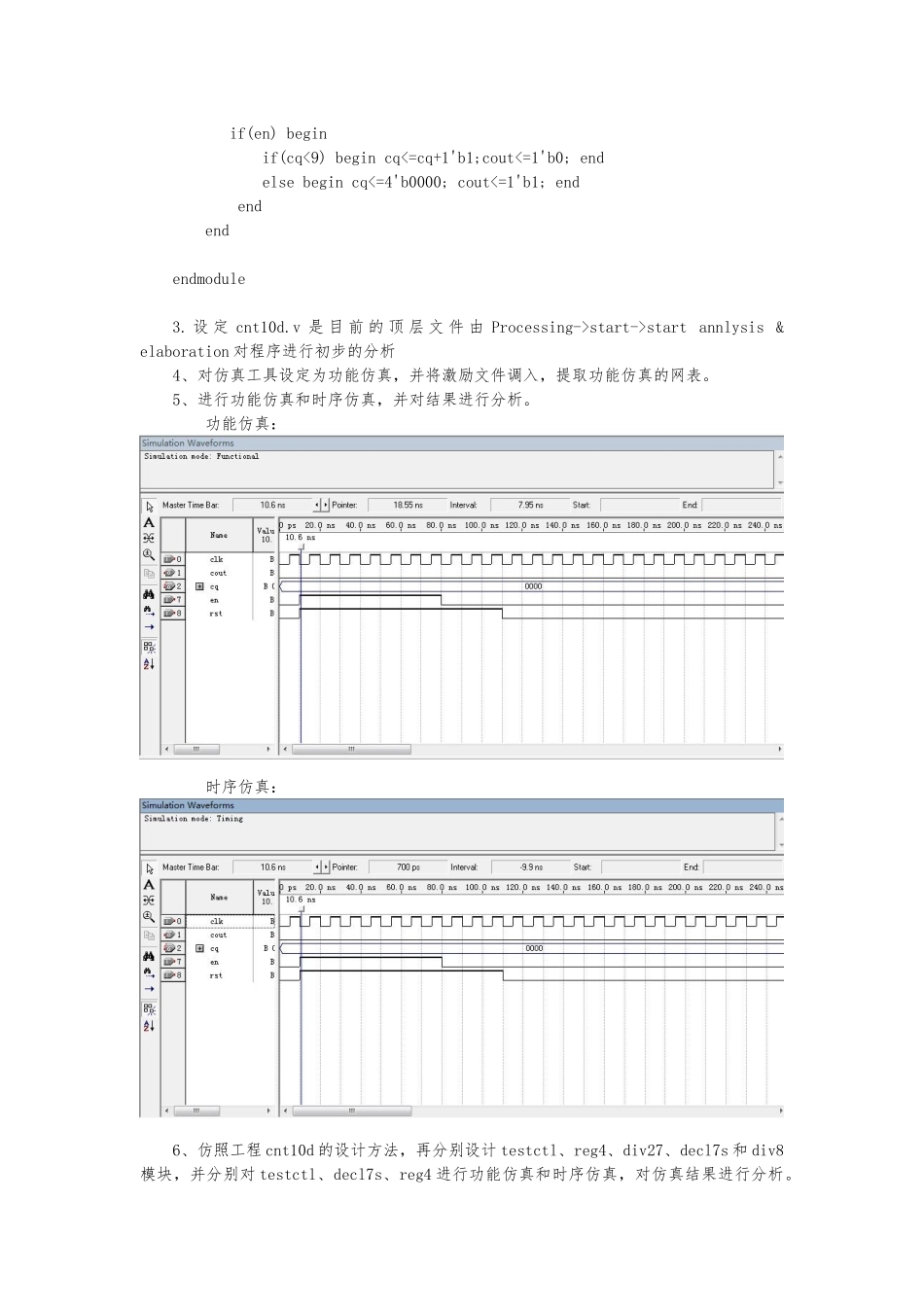

西 南 科 技 大 学电工学,电子技术学生实验报告课程名称 FPGA 现代数字系统设计 实验名称 4 位十进制频率计设计 姓 名 邓 彪 班 级电子 0902 指导老师 评 分 2024 年 4 月 10 日1.实验目的:设计 4 位十进制频率计,学习较复杂的数字系统设计方法。2.实验原理: 根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为 1 秒的对输入信号脉冲计数允许的信号;1 秒计数完毕后,计数值锁入锁存器的锁存信号和为下一测频计数周期作准备的计数器清 0 信号。这清 0 个信号可以由一个测频控制信号发生器产生,即图 5-1 中的 TESTCTL,它的设计要,TESTCTL 的计数使能信号 CNT_EN 能产生一个 1 秒脉宽的周期信号,并对频率计的每一计数器 CNT10 的 EN 使能端进行同步控制。当 CNT_EN 高电平常,允许计数;低电平常停止计数,并保持其所计的脉冲数。在停止计数期间,首先需要一个锁存信号 LOAD 的上跳沿将计数器在前 1 秒钟的计数值锁存进各锁存器 REG4B 中,并由外部的 7 段译码器译出,显示计数值。设置锁存器的好处是,显示的数据稳定,不会由于周期性的清零信号而不断闪耀。锁存信号之后,必须有一清零信号 RST_CNT 对计数器进行清零,为下 1 秒钟的计数操作作准备。3.实验容:1、根据例 5-1(10 进制计数器,用于计算分频结果,并连接数码管显示)、例 5-2(测频控制器,使得频率计能自动测频)、例 5-3(锁存器,将频率计的每位数锁存后输出)以与 4 位十进制频率计的工作原理写出频率计的顶层文件(或者原理图),并给出其测频时序波形,与其分析。在测试时候添加以下两个模块: (1)DE2 上有两个时钟源,分别是(50MHZ ,PIN_N2),(27MHz,PIN_D13),编写一个分频模块,分别产生测频器的 clk(8Hz)和 f_in(频率任意定)时钟,用于连接在DE2 上进行测试。(2)编写数码显示模块 led7s,用于显示频率计数的结果显示。2、频率计设计硬件验证。编译、综合和适配频率计顶层设计文件,并编程下载进入目标器件中。4.实验步骤:1. 构建一个工程名是我的学号 f_test。2 、 输 入 cnt10d 的 Verilog 文 本 , 将 设 计 的 Verilog 程 序 输 入 , 并 存 盘 名 为cnt10d.v,将波形文件存盘为 cnt10d.vwf。modulet10d(clk,rst,en,cq,cout); input clk; input rst; input en; output[3:0] cq; output cout; reg[3:0] cq;...