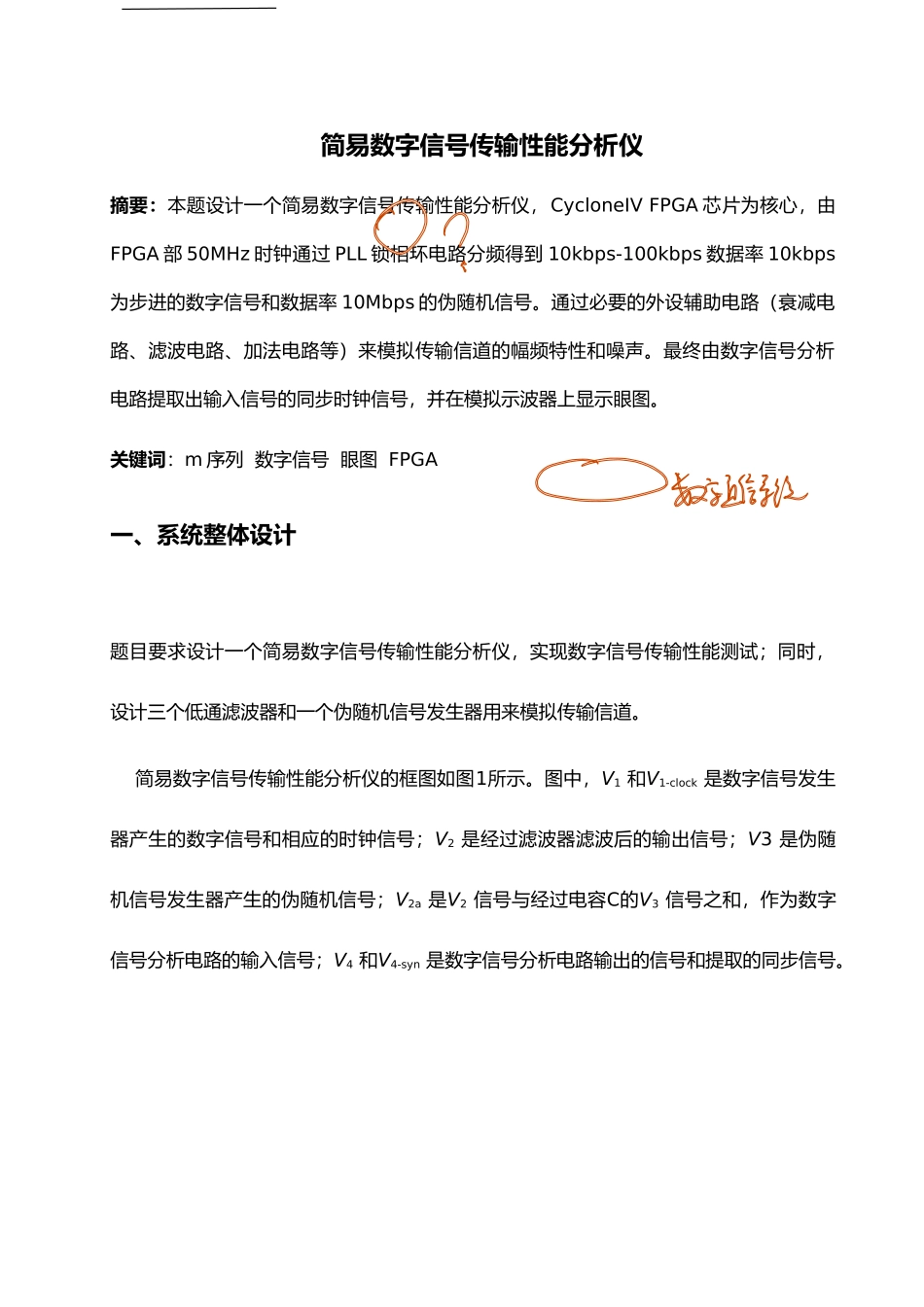

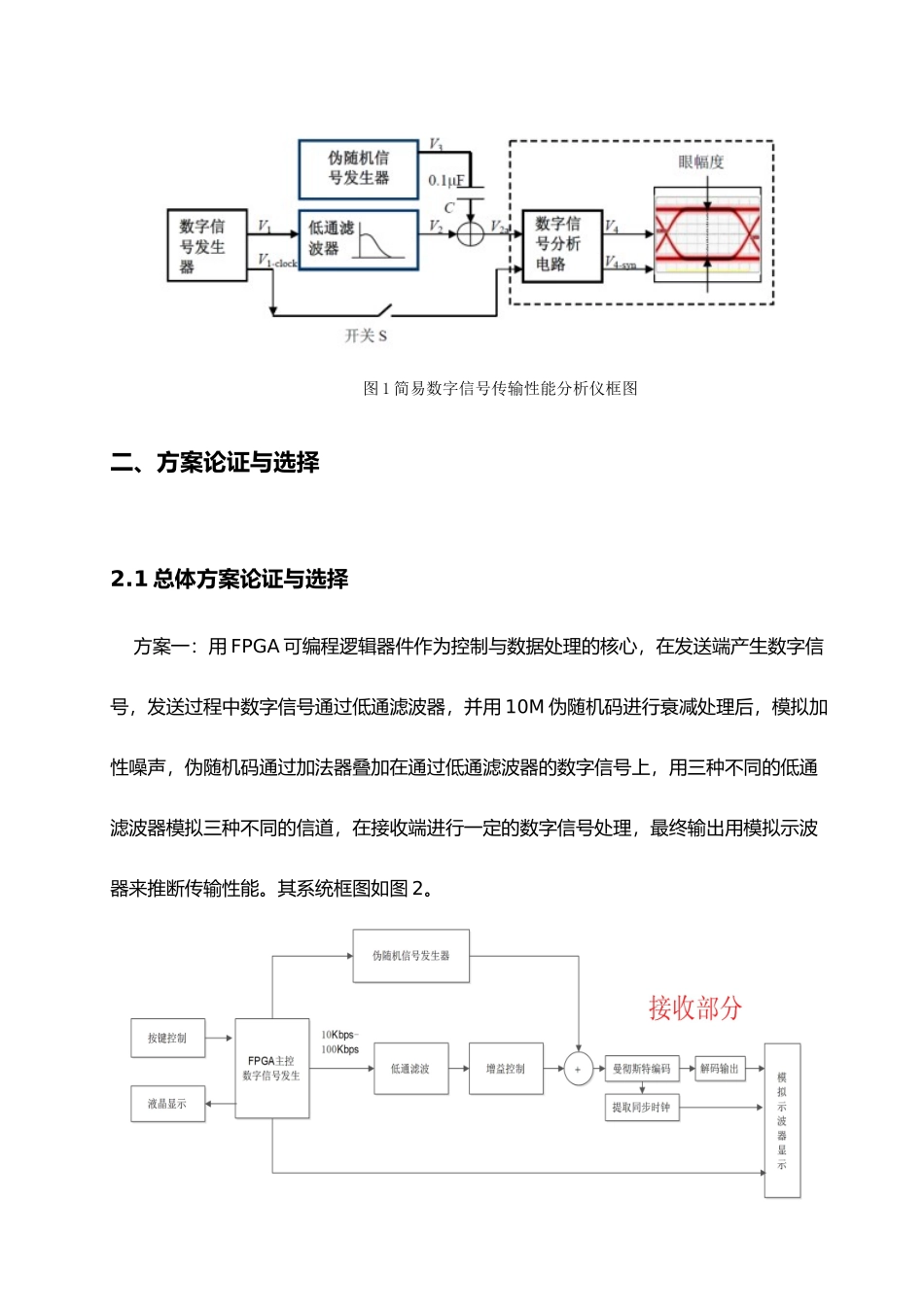

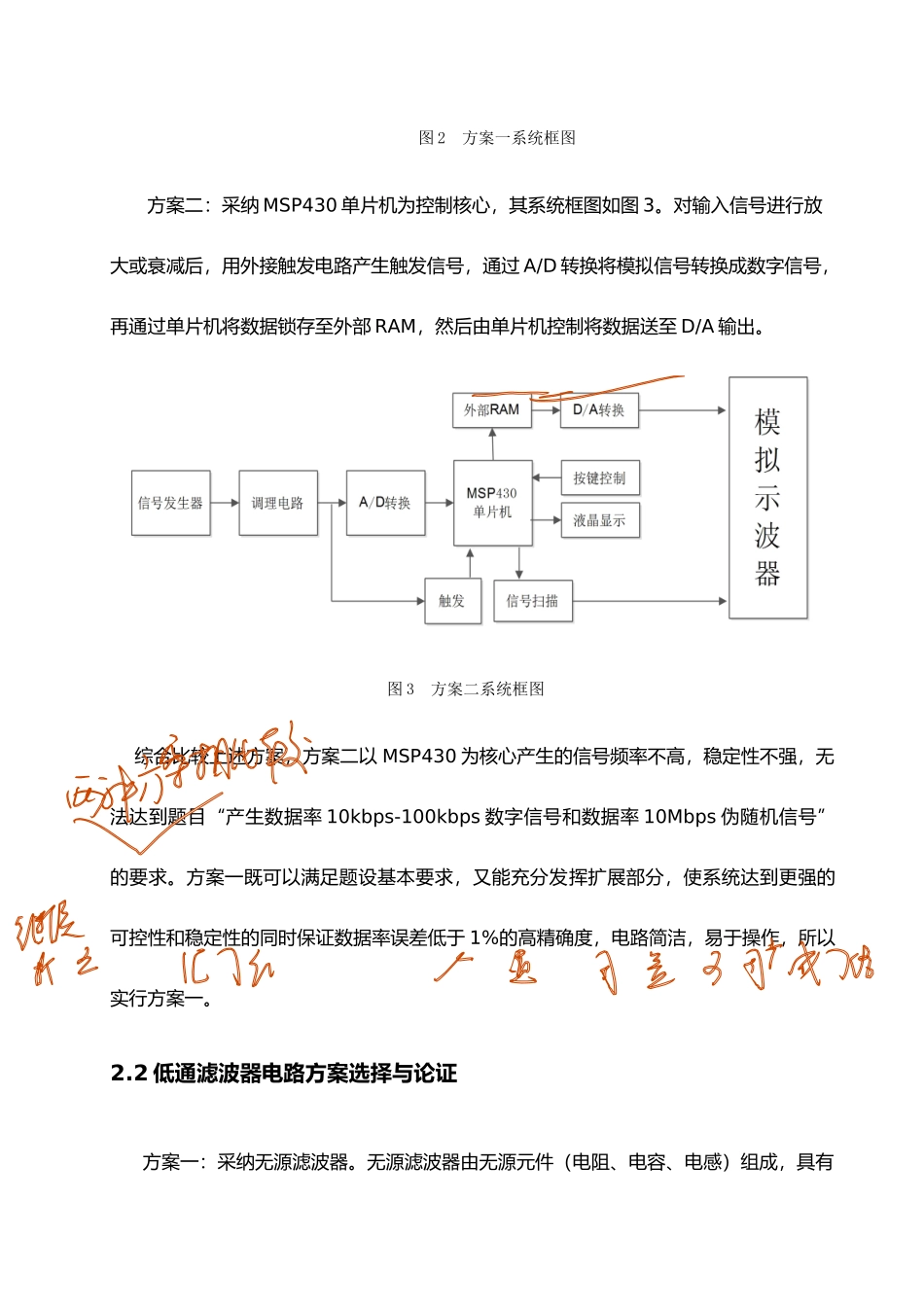

简易数字信号传输性能分析仪摘要:本题设计一个简易数字信号传输性能分析仪,CycloneIV FPGA 芯片为核心,由FPGA 部 50MHz 时钟通过 PLL 锁相环电路分频得到 10kbps-100kbps 数据率 10kbps为步进的数字信号和数据率 10Mbps 的伪随机信号。通过必要的外设辅助电路(衰减电路、滤波电路、加法电路等)来模拟传输信道的幅频特性和噪声。最终由数字信号分析电路提取出输入信号的同步时钟信号,并在模拟示波器上显示眼图。关键词:m 序列 数字信号 眼图 FPGA一、系统整体设计题目要求设计一个简易数字信号传输性能分析仪,实现数字信号传输性能测试;同时,设计三个低通滤波器和一个伪随机信号发生器用来模拟传输信道。 简易数字信号传输性能分析仪的框图如图1所示。图中,V1 和V1-clock 是数字信号发生器产生的数字信号和相应的时钟信号;V2 是经过滤波器滤波后的输出信号;V3 是伪随机信号发生器产生的伪随机信号;V2a 是V2 信号与经过电容C的V3 信号之和,作为数字信号分析电路的输入信号;V4 和V4-syn 是数字信号分析电路输出的信号和提取的同步信号。二、方案论证与选择2.1 总体方案论证与选择 方案一:用 FPGA 可编程逻辑器件作为控制与数据处理的核心,在发送端产生数字信号,发送过程中数字信号通过低通滤波器,并用 10M 伪随机码进行衰减处理后,模拟加性噪声,伪随机码通过加法器叠加在通过低通滤波器的数字信号上,用三种不同的低通滤波器模拟三种不同的信道,在接收端进行一定的数字信号处理,最终输出用模拟示波器来推断传输性能。其系统框图如图 2。图 1 简易数字信号传输性能分析仪框图方案二:采纳 MSP430 单片机为控制核心,其系统框图如图 3。对输入信号进行放大或衰减后,用外接触发电路产生触发信号,通过 A/D 转换将模拟信号转换成数字信号,再通过单片机将数据锁存至外部 RAM,然后由单片机控制将数据送至 D/A 输出。 综合比较上述方案,方案二以 MSP430 为核心产生的信号频率不高,稳定性不强,无法达到题目“产生数据率 10kbps-100kbps 数字信号和数据率 10Mbps 伪随机信号”的要求。方案一既可以满足题设基本要求,又能充分发挥扩展部分,使系统达到更强的可控性和稳定性的同时保证数据率误差低于 1%的高精确度,电路简洁,易于操作,所以实行方案一。 2.2 低通滤波器电路方案选择与论证方案一:采纳无源滤波器。无源滤波器由无源元件(电阻、电容、电感)组成,具有...