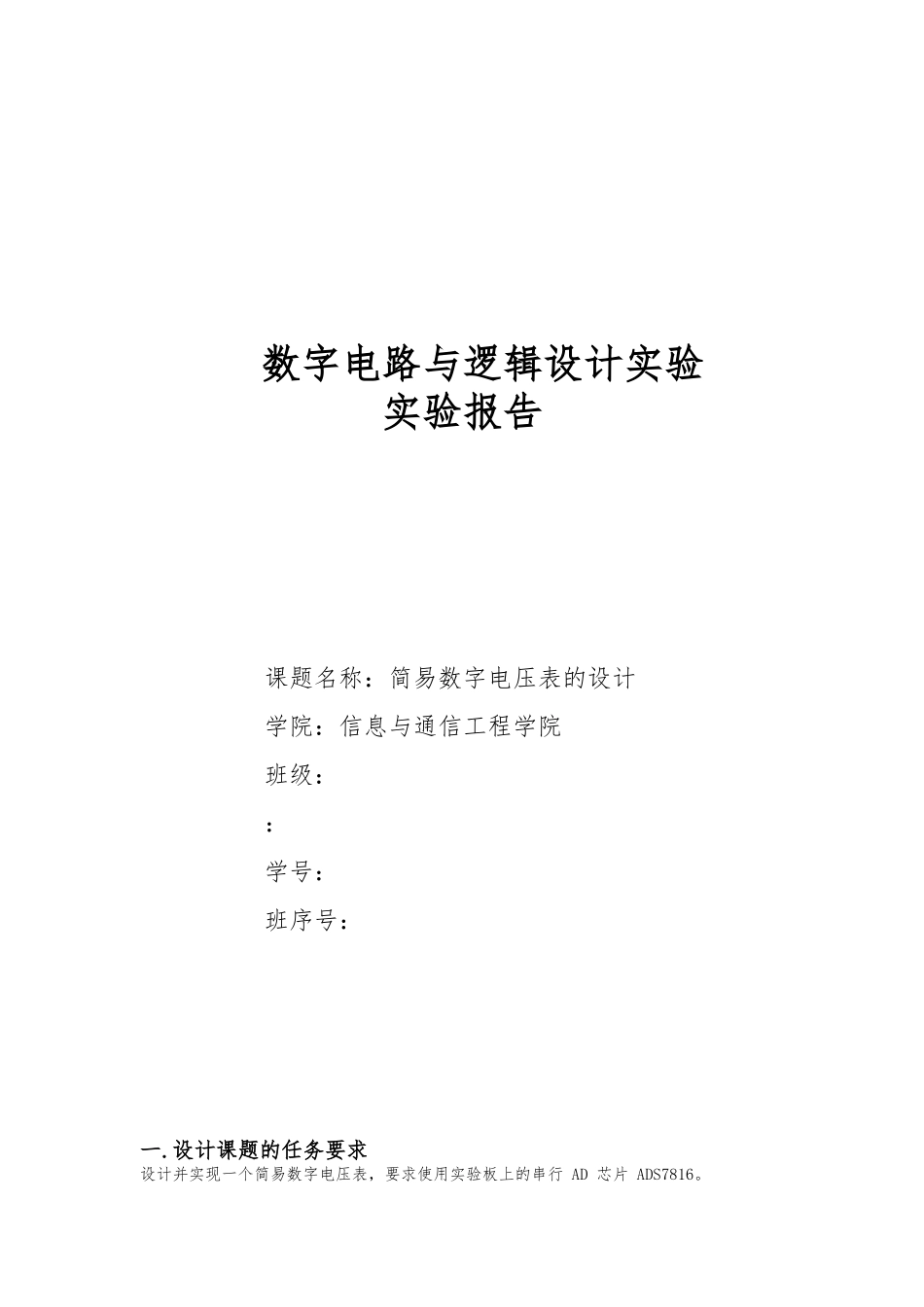

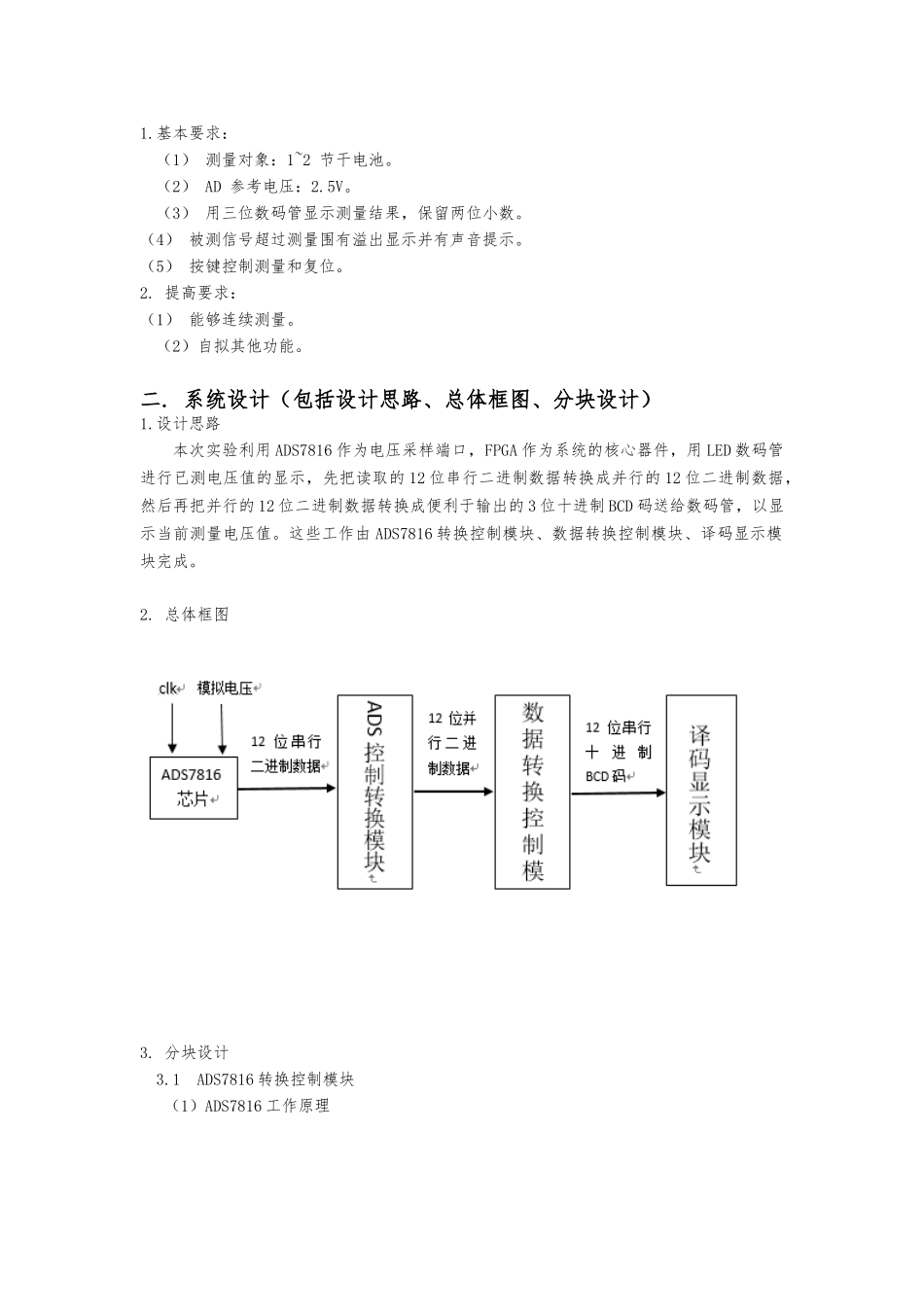

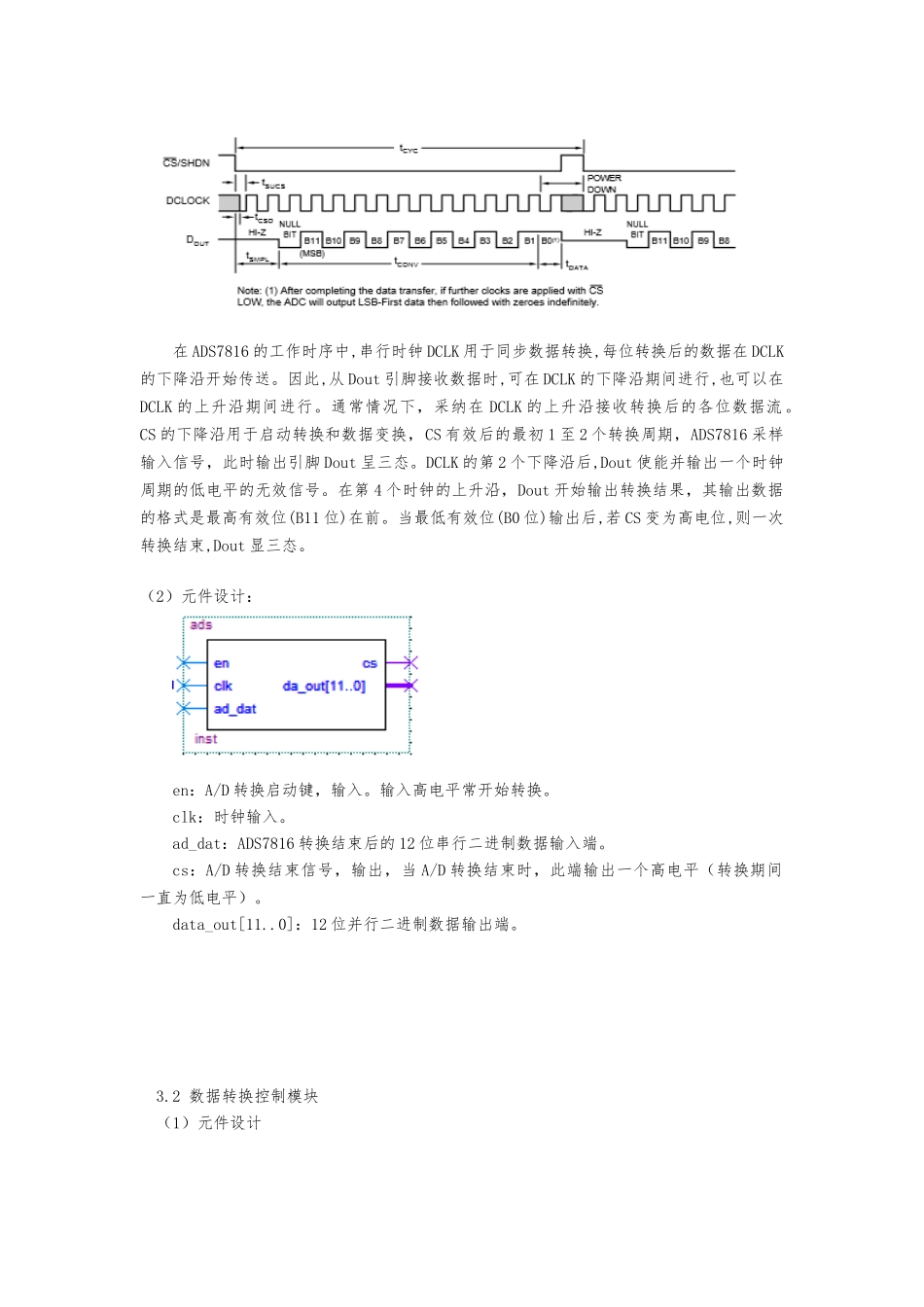

数字电路与逻辑设计实验 实验报告课题名称:简易数字电压表的设计学院:信息与通信工程学院班级::学号:班序号: 一.设计课题的任务要求设计并实现一个简易数字电压表,要求使用实验板上的串行 AD 芯片 ADS7816。1.基本要求:(1) 测量对象:1~2 节干电池。 (2) AD 参考电压:2.5V。 (3) 用三位数码管显示测量结果,保留两位小数。(4) 被测信号超过测量围有溢出显示并有声音提示。(5) 按键控制测量和复位。2. 提高要求:(1) 能够连续测量。(2)自拟其他功能。二. 系统设计(包括设计思路、总体框图、分块设计)1.设计思路本次实验利用 ADS7816 作为电压采样端口,FPGA 作为系统的核心器件,用 LED 数码管进行已测电压值的显示,先把读取的 12 位串行二进制数据转换成并行的 12 位二进制数据,然后再把并行的 12 位二进制数据转换成便利于输出的 3 位十进制 BCD 码送给数码管,以显示当前测量电压值。这些工作由 ADS7816 转换控制模块、数据转换控制模块、译码显示模块完成。2. 总体框图3. 分块设计3.1 ADS7816 转换控制模块 (1)ADS7816 工作原理在 ADS7816 的工作时序中,串行时钟 DCLK 用于同步数据转换,每位转换后的数据在 DCLK的下降沿开始传送。因此,从 Dout 引脚接收数据时,可在 DCLK 的下降沿期间进行,也可以在DCLK 的上升沿期间进行。通常情况下,采纳在 DCLK 的上升沿接收转换后的各位数据流。CS 的下降沿用于启动转换和数据变换,CS 有效后的最初 1 至 2 个转换周期,ADS7816 采样输入信号,此时输出引脚 Dout 呈三态。DCLK 的第 2 个下降沿后,Dout 使能并输出一个时钟周期的低电平的无效信号。在第 4 个时钟的上升沿,Dout 开始输出转换结果,其输出数据的格式是最高有效位(B11 位)在前。当最低有效位(B0 位)输出后,若 CS 变为高电位,则一次转换结束,Dout 显三态。(2)元件设计:en:A/D 转换启动键,输入。输入高电平常开始转换。clk:时钟输入。ad_dat:ADS7816 转换结束后的 12 位串行二进制数据输入端。cs:A/D 转换结束信号,输出,当 A/D 转换结束时,此端输出一个高电平(转换期间一直为低电平)。data_out[11..0]:12 位并行二进制数据输出端。3.2 数据转换控制模块(1)元件设计en:开始测量键,输入。按键按下为高电平。reset:复位键,输入。按键按下为高电平。clk:时钟输入。datain[11..0]:12 位并行二进制数据输入...