第二章设计方案论证2

1整个系统的原理整个系统的设计方案如下面的介绍,主要是,系统原理,控制芯片介绍和管脚的说明

1系统原理说明图2

1系统原理框图从上面的框图我们很容易的可以看出,CPU是整个电路的核心,它受电源驱动,然后驱动555电路和液晶屏,并且反馈到上位机

整个设计的大体思想就是这样,CPU作为最核心的部件,是这给那个电路的主体,也是整个电路的控制部分

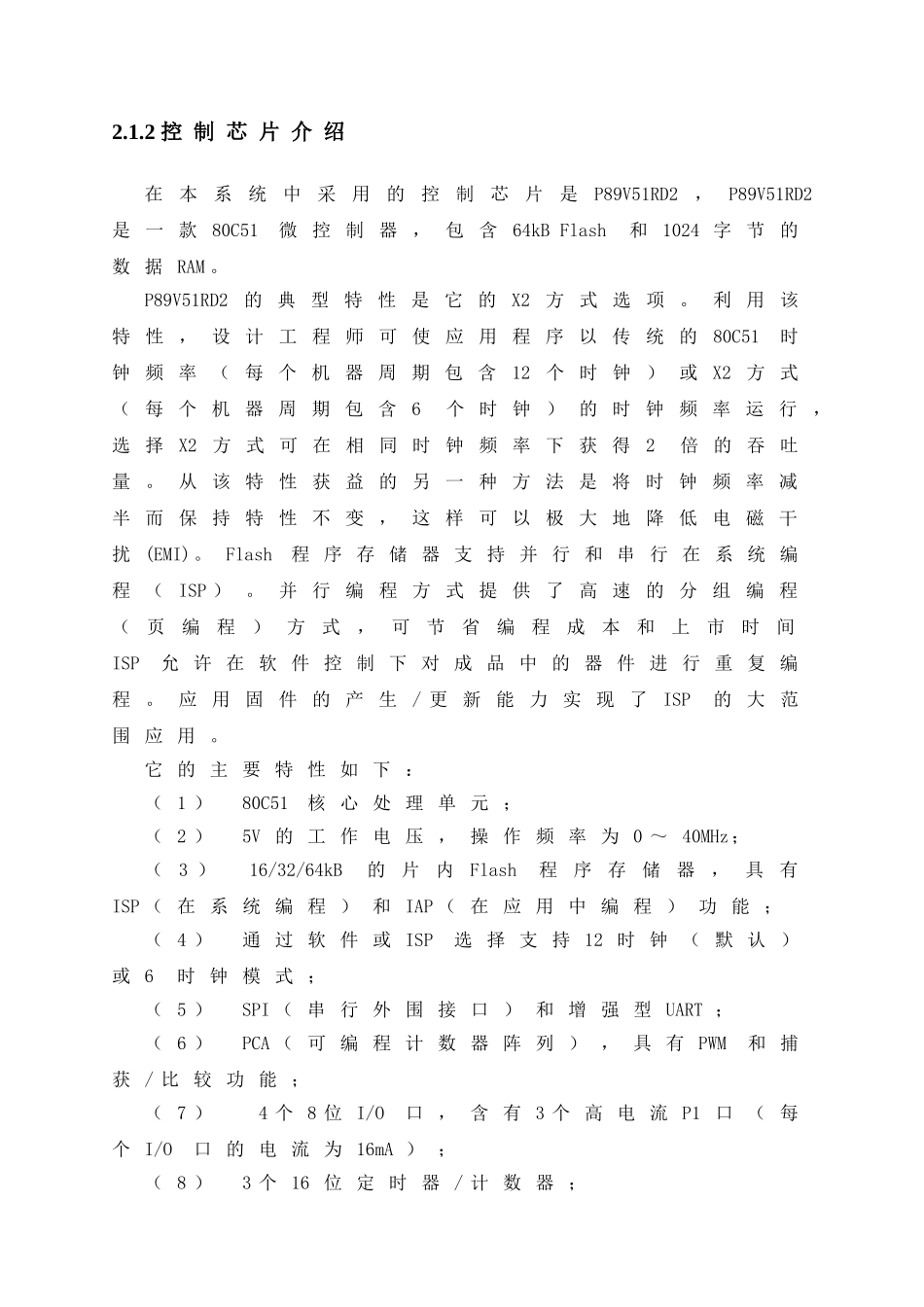

此次我们采用的是由飞利浦公司生产的P89V5RD2HBA单片机芯片

芯片的引脚图如图2

本设计工作,我主要负责的是软件的编程的工作,这就需要对所用的主芯片要有一个详实的了解,下面是我们在此次设计中用到的芯片口的详细资料,(说明,本次设计中P2口没有用到,作为红外线报警器的扩展口来用,以备今后对红外线的升级之用

2控制芯片介绍在本系统中采用的控制芯片是P89V51RD2,P89V51RD2是一款80C51微控制器,包含64kBFlash和1024字节的数据RAM

P89V51RD2的典型特性是它的X2方式选项

利用该特性,设计工程师可使应用程序以传统的80C51时钟频率(每个机器周期包含12个时钟)或X2方式(每个机器周期包含6个时钟)的时钟频率运行,选择X2方式可在相同时钟频率下获得2倍的吞吐量

从该特性获益的另一种方法是将时钟频率减半而保持特性不变,这样可以极大地降低电磁干扰(EMI)

Flash程序存储器支持并行和串行在系统编程(ISP)

并行编程方式提供了高速的分组编程(页编程)方式,可节省编程成本和上市时间ISP允许在软件控制下对成品中的器件进行重复编程

应用固件的产生/更新能力实现了ISP的大范围应用

它的主要特性如下:(1)80C51核心处理单元;(2)5V的工作电压,操作频率为0~40MHz;(3)16/32/64kB的片内Flash程序存储器,具有ISP(在系统编程)和IAP