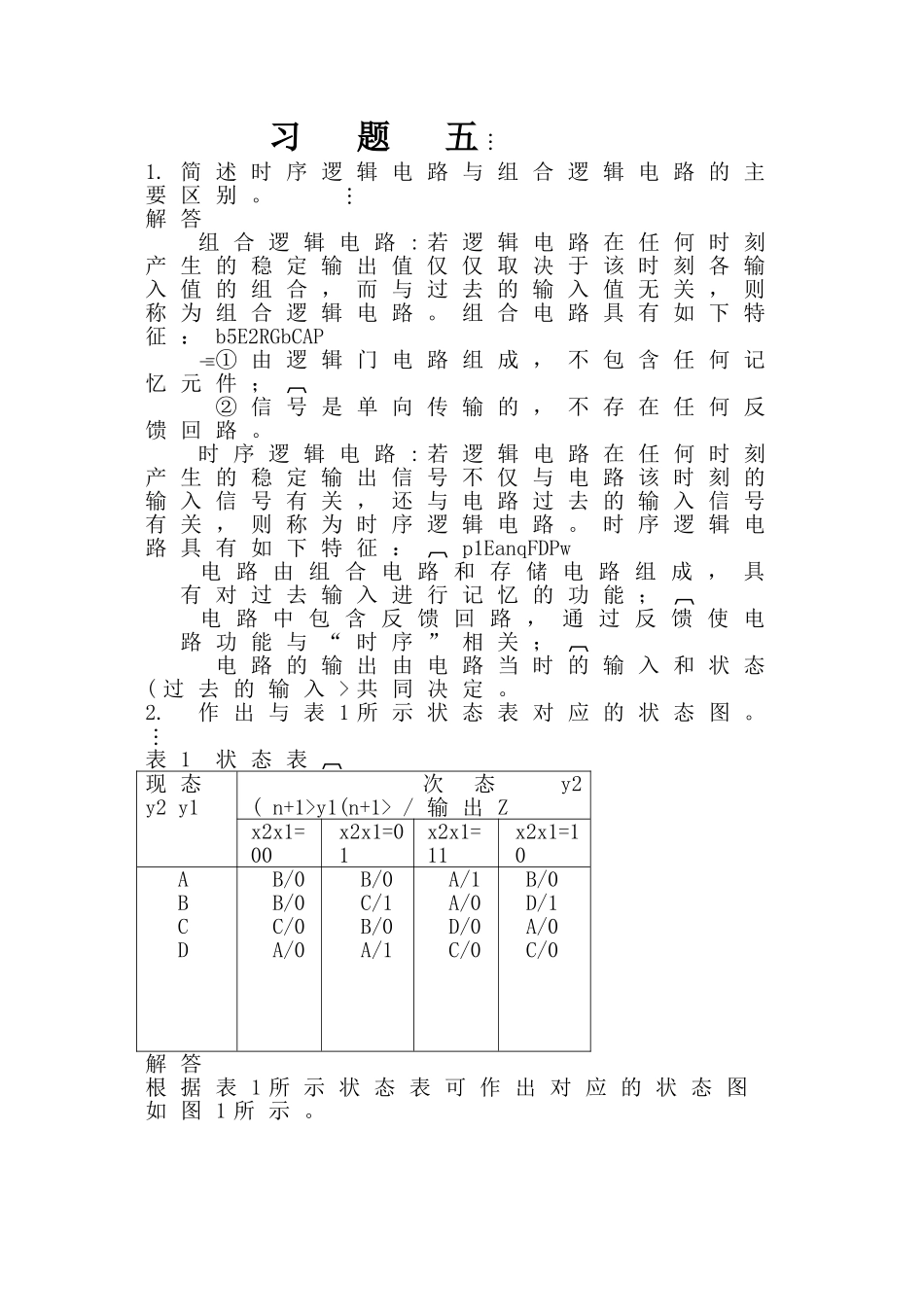

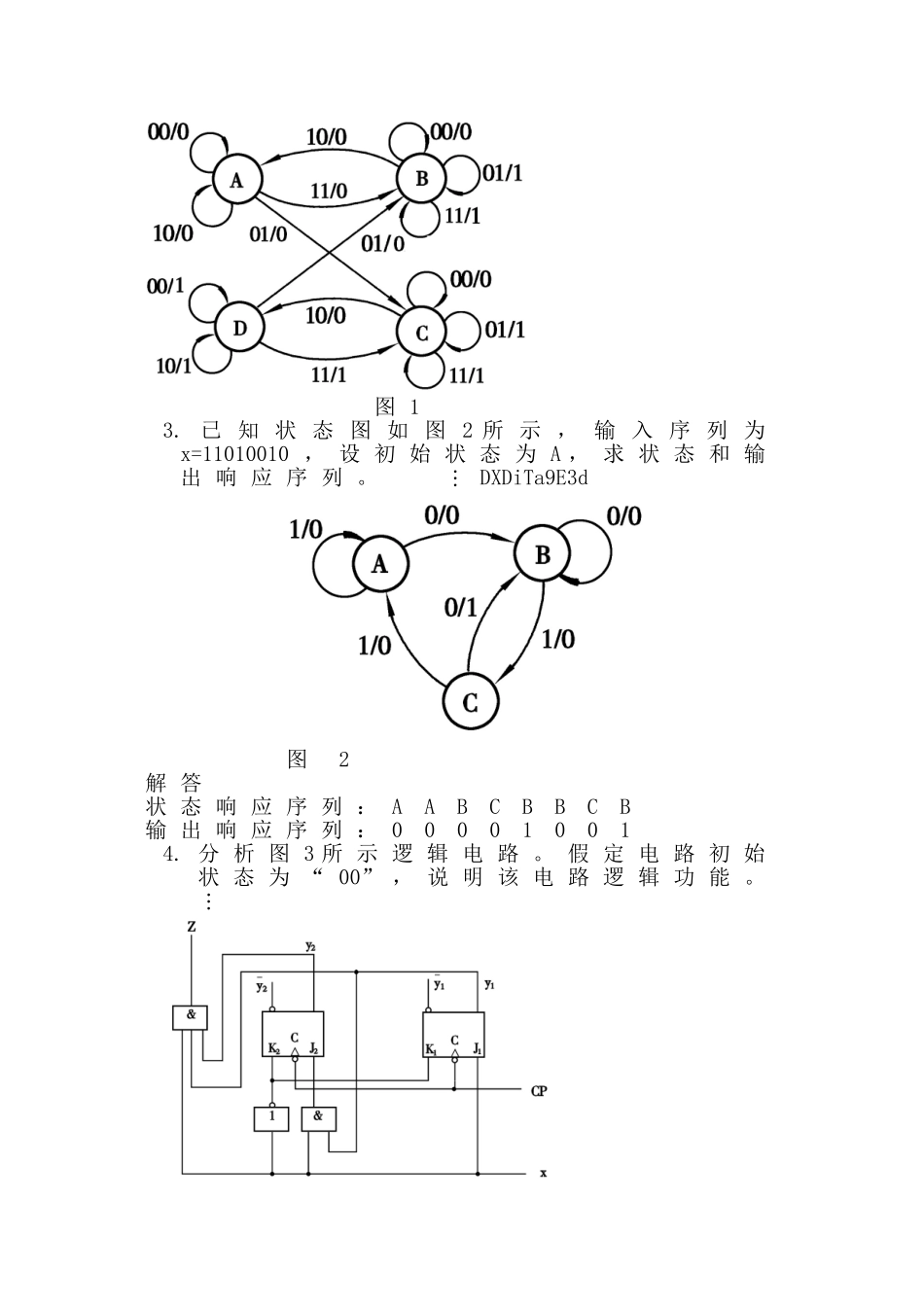

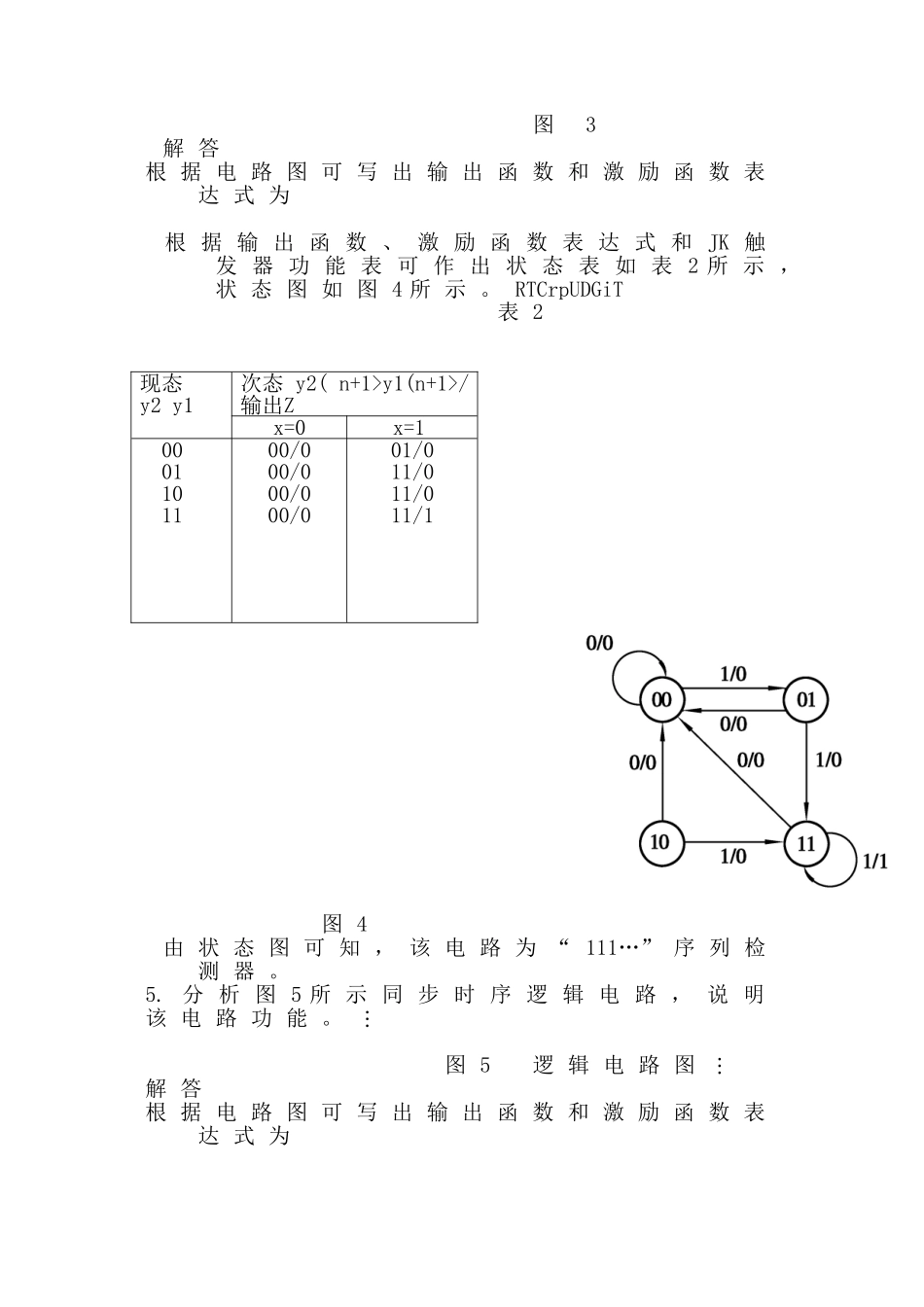

习题五1.简述时序逻辑电路与组合逻辑电路的主要区别。解答组合逻辑电路:若逻辑电路在任何时刻产生的稳定输出值仅仅取决于该时刻各输入值的组合,而与过去的输入值无关,则称为组合逻辑电路。组合电路具有如下特征:b5E2RGbCAP①由逻辑门电路组成,不包含任何记忆元件;②信号是单向传输的,不存在任何反馈回路。时序逻辑电路:若逻辑电路在任何时刻产生的稳定输出信号不仅与电路该时刻的输入信号有关,还与电路过去的输入信号有关,则称为时序逻辑电路。时序逻辑电路具有如下特征:p1EanqFDPw电路由组合电路和存储电路组成,具有对过去输入进行记忆的功能;电路中包含反馈回路,通过反馈使电路功能与“时序”相关;电路的输出由电路当时的输入和状态(过去的输入>共同决定。2.作出与表1所示状态表对应的状态图。表1状态表现态y2y1次态y2(n+1>y1(n+1>/输出Zx2x1=00x2x1=01x2x1=11x2x1=10ABCDB/0B/0C/0A/0B/0C/1B/0A/1A/1A/0D/0C/0B/0D/1A/0C/0解答根据表1所示状态表可作出对应的状态图如图1所示。图13.已知状态图如图2所示,输入序列为x=11010010,设初始状态为A,求状态和输出响应序列。DXDiTa9E3d图2解答状态响应序列:AABCBBCB输出响应序列:000010014.分析图3所示逻辑电路。假定电路初始状态为“00”,说明该电路逻辑功能。图3解答根据电路图可写出输出函数和激励函数表达式为根据输出函数、激励函数表达式和JK触发器功能表可作出状态表如表2所示,状态图如图4所示。RTCrpUDGiT表2图4由状态图可知,该电路为“111…”序列检测器。5.分析图5所示同步时序逻辑电路,说明该电路功能。图5逻辑电路图解答根据电路图可写出输出函数和激励函数表达式为现态y2y1次态y2(n+1>y1(n+1>/输出Zx=0x=10001101100/000/000/000/001/011/011/011/1根据输出函数、激励函数表达式和D触发器功能表可作出状态表如表3所示,状态图如图6所示。5PCzVD7HxA表3图6由状态图可知,该电路是一个三进制可逆计数器(又称模3可逆计数器>,当x=0时实现加1计数,当x=1时实现减1计数。jLBHrnAILg6.分析图7所示逻辑电路,说明该电路功能。现态y2y1次态y2(n+1>y1(n+1>/输出Zx=0x=10001101101/011/001/000/111/100/011/001/0图7逻辑电路图解答根据电路图可写出输出函数和激励函数表达式为根据输出函数、激励函数表达式和JK触发器功能表可作出状态表如表4所示,状态图如图8所示。xHAQX74J0X表4现态y2y1次态y2(n+1>y1(n+1>/输出Zx=0x=10001101101/010/011/000/111/100/001/010/1图8由状态图可知,该电路是一个模四可逆计数器。当x=0时实现加1计数,输出Z为进位信号;当x=1时实现减1计数,输出Z为借位信号。LDAYtRyKfE7.作出“0101”序列检测器的Mealy型状态图和Moore型状态图。典型输入、输出序列如下。Zzz6ZB2Ltk输入x:110101010011输出Z:000001010000解答根据典型输入、输出序列,可作出“0101”序列检测器的Mealy型状态图和Moore型状态图分别如图9、图10所示.dvzfvkwMI1图9Mealy型状态图图10Moore型状态图8.设计一个代码检测器,该电路从输入端x串行输入余3码(先低位后高位>,当出现非法数字时,电路输出Z为1,否则输出为0。试作出Mealy型状态图。rqyn14ZNXI解答根据题意,可作出Mealy型状态图如图11所示。图119.化简表5所示原始状态表。表5原始状态表解答根据状态等效判断法则,可利用隐含表求出状态等效对

(B,D>(C,F>(E,G>;EmxvxOtOco最大等效类为{A,B,D}、{CF}、{E,G};令A,B,D}→a、{CF}→b、{E,G}→c,可得最简状态表如表6所示。SixE2yXPq5表6最简状态表10.化简表7所示不完全确定原始状态表。现态次态/输出Zx=0x=1ABCDEFGB/0A/0F/0A/0A/0C/0A/0C/0F/0G/0C/0A/1E/0B/1现态次态/输出Zx=0x=1abca/0b/0a/0b/0c/0a/1表7原始状态表解答根据状态相容判断法则,可利用隐含表求出状态相容对、(C,E>、(B,C>、(B,E>;6ewMyirQFL利用覆盖闭合表可求出最小闭覆盖为{A,B}、{A,D}、{B,C,E};kavU42VRUs令{A,B}→a、{A,D}→b、{B,C,E}→c,可得最简状态表如表8所示。y6v3ALoS89表811.按照相邻法编码原则对表9进行状态编码。表9状态表解答给定状态表中有4个状态,状...