1数字电子技术基础实验报告题目:实验三时序电路设计小组成员:小组成员:2实验三时序电路设计一、实验目的1

熟悉使用 QuartusII 软件内嵌函数,实现脉冲信号;2•了解掌握实验开发板上数码管和 LED 部分3

强化对 74161 二进制计数器、7447 七段译码器、74194 移位寄存器的理解和应用

二、实验要求要 求 1 : 参 照 参 考 内 容 , 用 Quartusll 软 件 内 嵌 函 数ipm_counter 实现 50M 分频,输出频率为 1Hz 秒脉冲信号,用实验板上绿色 LED 灯观察

要求 2:参照参考内容中数码管显示控制电路设计方法,用 74161 二进制计数器、7447 七段译码器和若干门电路,用原理图输入方法实现一个七段数码管上显示 0、1、2、3、4、5、0、2、4、1、3、5

要求 3:参照参考内容,用 74161 二进制计数器、74194 移位寄存器和若干门电路,用原理图输入方法实现彩灯控制器电路设计

验收要求:将要求 2 和要求 3 同时在电路上实现,验收时能够说明电路设计的原理

注:如果电脑软件出现 Megafunction 无法启用,可利用绑定按键开关作为时钟信号,验收时需要演示波形仿真结果

三、实验设备1)电脑一台;2)数字电路实验箱;3)数据线一根

(4)EDO 实验开发板一个四、实验原理要求 1:(1)用 Quartusll 软件内嵌函数 ipm_counter 实现 50M 分频,3输出频率为1Hz 秒脉冲信号,并用实验板上绿色LED 灯观察

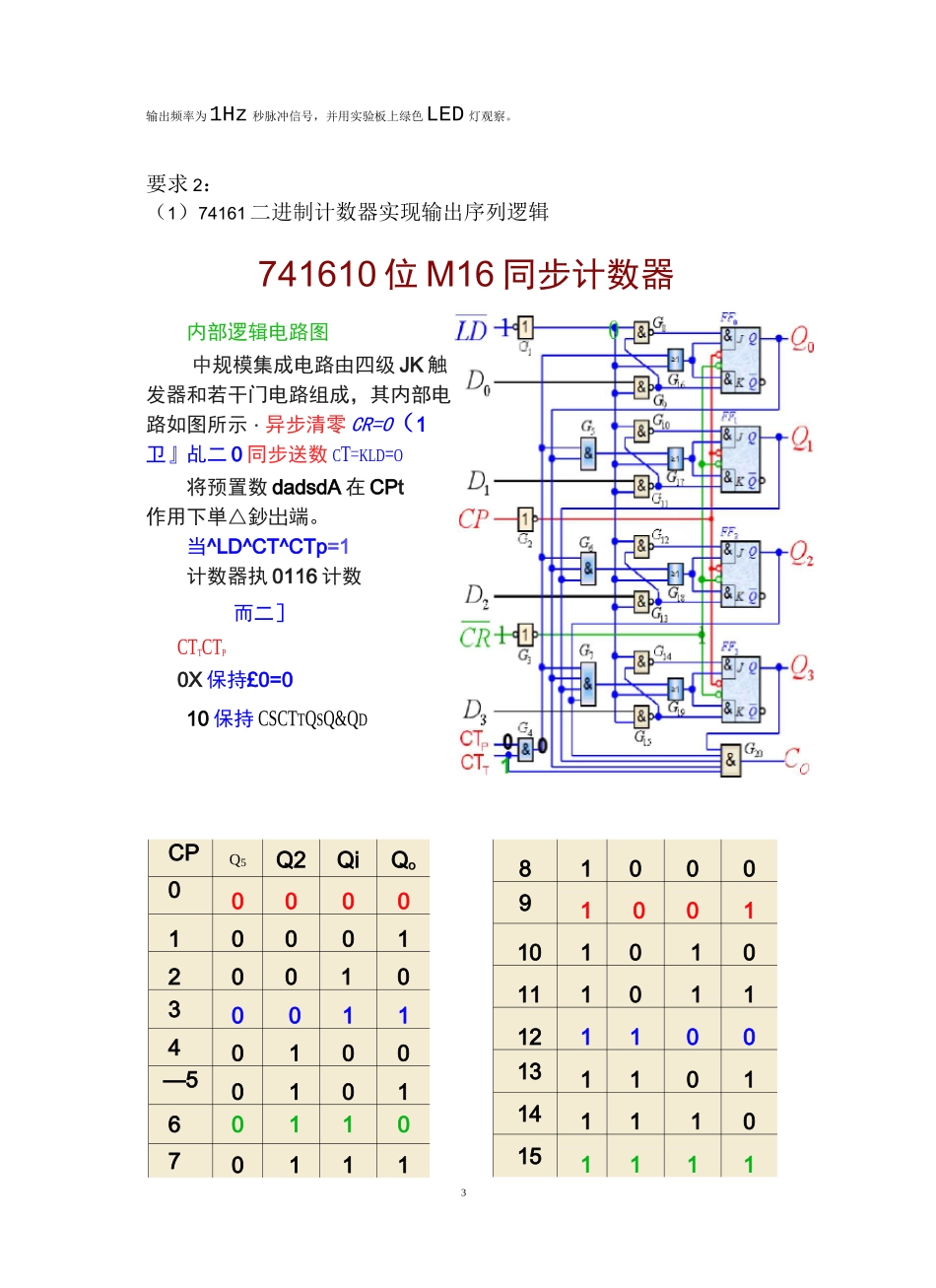

要求 2:(1)74161 二进制计数器实现输出序列逻辑741610 位 M16 同步计数器内部逻辑电路图中规模集成电路由四级 JK 触发器和若干门电路组成,其内部电路如图所示・异步清零 CR=O(1卫』乩二 0 同步送数 CT=KLD=O将预置数 dadsdA 在 CPt作用下単