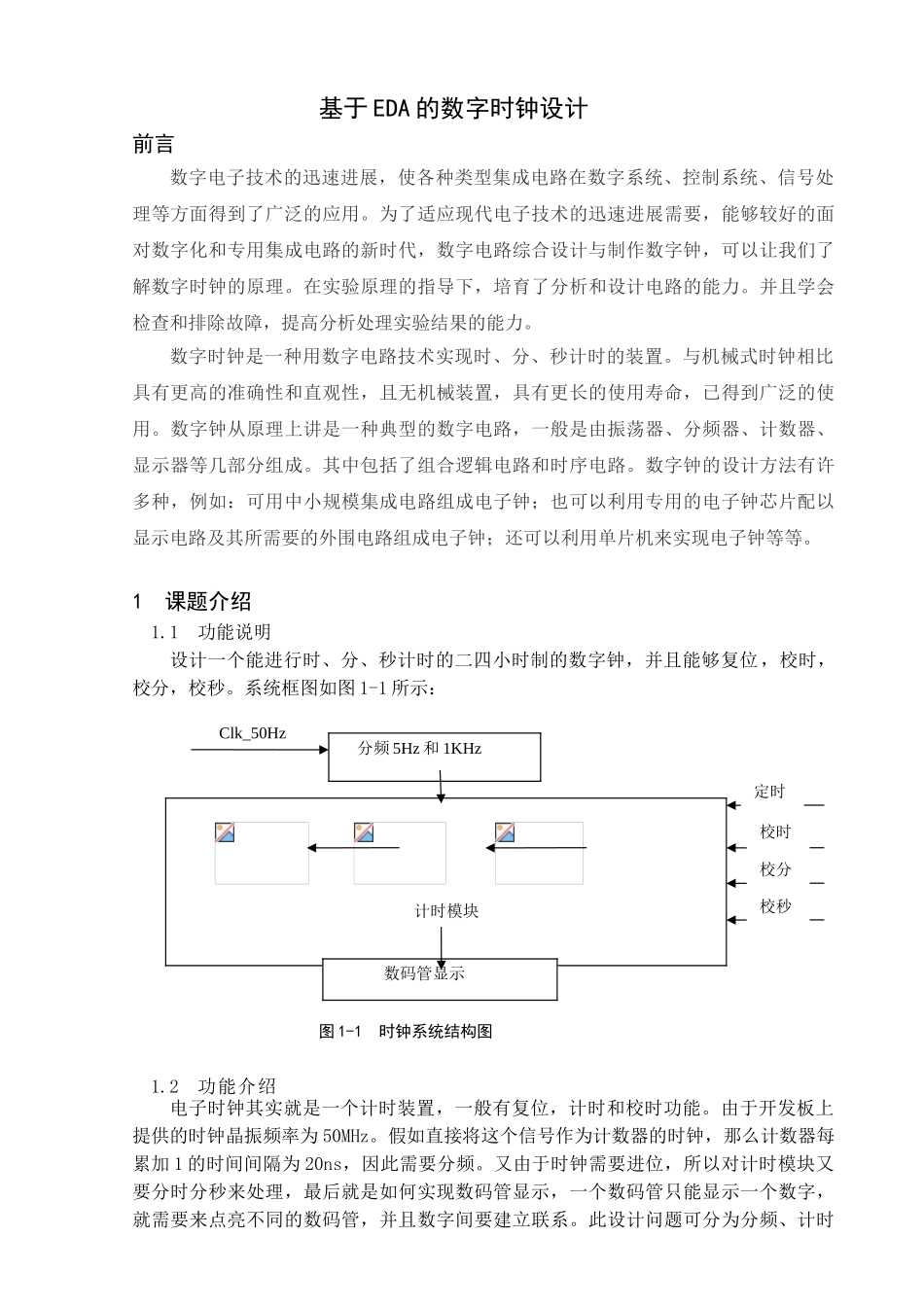

基于 EDA 的数字时钟设计前言 数字电子技术的迅速进展,使各种类型集成电路在数字系统、控制系统、信号处理等方面得到了广泛的应用。为了适应现代电子技术的迅速进展需要,能够较好的面对数字化和专用集成电路的新时代,数字电路综合设计与制作数字钟,可以让我们了解数字时钟的原理。在实验原理的指导下,培育了分析和设计电路的能力。并且学会检查和排除故障,提高分析处理实验结果的能力。数字时钟是一种用数字电路技术实现时、分、秒计时的装置。与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更长的使用寿命,已得到广泛的使用。数字钟从原理上讲是一种典型的数字电路,一般是由振荡器、分频器、计数器、显示器等几部分组成。其中包括了组合逻辑电路和时序电路。数字钟的设计方法有许多种,例如:可用中小规模集成电路组成电子钟;也可以利用专用的电子钟芯片配以显示电路及其所需要的外围电路组成电子钟;还可以利用单片机来实现电子钟等等。 1 课题介绍1.1 功能说明设计一个能进行时、分、秒计时的二四小时制的数字钟,并且能够复位,校时,校分,校秒。系统框图如图 1-1 所示:图 1-1 时钟系统结构图1.2 功能介绍电子时钟其实就是一个计时装置,一般有复位,计时和校时功能。由于开发板上提供的时钟晶振频率为 50MHz。假如直接将这个信号作为计数器的时钟,那么计数器每累加 1 的时间间隔为 20ns,因此需要分频。又由于时钟需要进位,所以对计时模块又要分时分秒来处理,最后就是如何实现数码管显示,一个数码管只能显示一个数字,就需要来点亮不同的数码管,并且数字间要建立联系。此设计问题可分为分频、计时分频 5Hz 和 1KHzClk_50Hz 计时模块数码管显示定时校时校分校秒模块和数码管显示三大部。 1.3 关于 EDA 和 Quartus IIEDA 是 电 子 设 计 自 动 化 ( Electronic Design Automation ) 的 缩 写 , 在20 世纪 60 年代中期从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念进展而来的。EDA 技术就是以计算机为工具,设计者在 EDA 软件平台上,用硬件描述语言 VHDL 完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。EDA 技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强...