电子综合设计基于 FPGA 的四路智能抢答器目录1.设计目的2.抢答器的特点3.设计的内容要求4.系统硬件原理图5.软件流程图6.系统电路图7.系统各模块设计分析8.原程序代码9.设计感想10.参考文献11.附录一、设计目的:通过本次电子综合设计,掌握了数字电路系统的设计方法,进一步学会了如何使用数字电路实现现实的电路系统;学会了如何运用硬件描述语言 VHDL 驱动数字硬件电路的工作,实现软硬件连调,以达到软硬件协同工作的目的;加强自主动手制作硬件以及编程实现所需现实功能的能力;二、抢答器的特点抢答器是为智力竞赛参赛者答题时进行抢答而设计的一种优先判决器电路,广泛应用于各种知识竞赛、文娱活动等场合

在各类竞赛中,特别是做抢答题时,在抢答过程中,为了知道哪一组或哪一名选手先答题,必须要有一个系统来完成这个任务

抢答过程中,只靠人的视觉是很难推断出哪组先答题

利用 FPGA 数字电路来设计抢答器,则可轻松解决这个问题

够实现抢答器功能的方式有多种,可以采纳模拟电路、数字电路或模拟与数字电路相结合的方式

早期的抢答器只由几个三极管、可控硅、发光管等组成, 能通过发光管的指示辨认出选手号码

现在大多数抢答器均使用数字集成电路,并增加了许多新功能,如选手号码显示、抢按前或抢按后的计时、选手得分显示功能

像这类抢答器,制作过程简单,准确性与可靠性高,而且安装维护简单

随着电子技术的进展,现在的抢答器功能越来越强,可靠性和准确性也越来越高

三、设计的内容要求:1

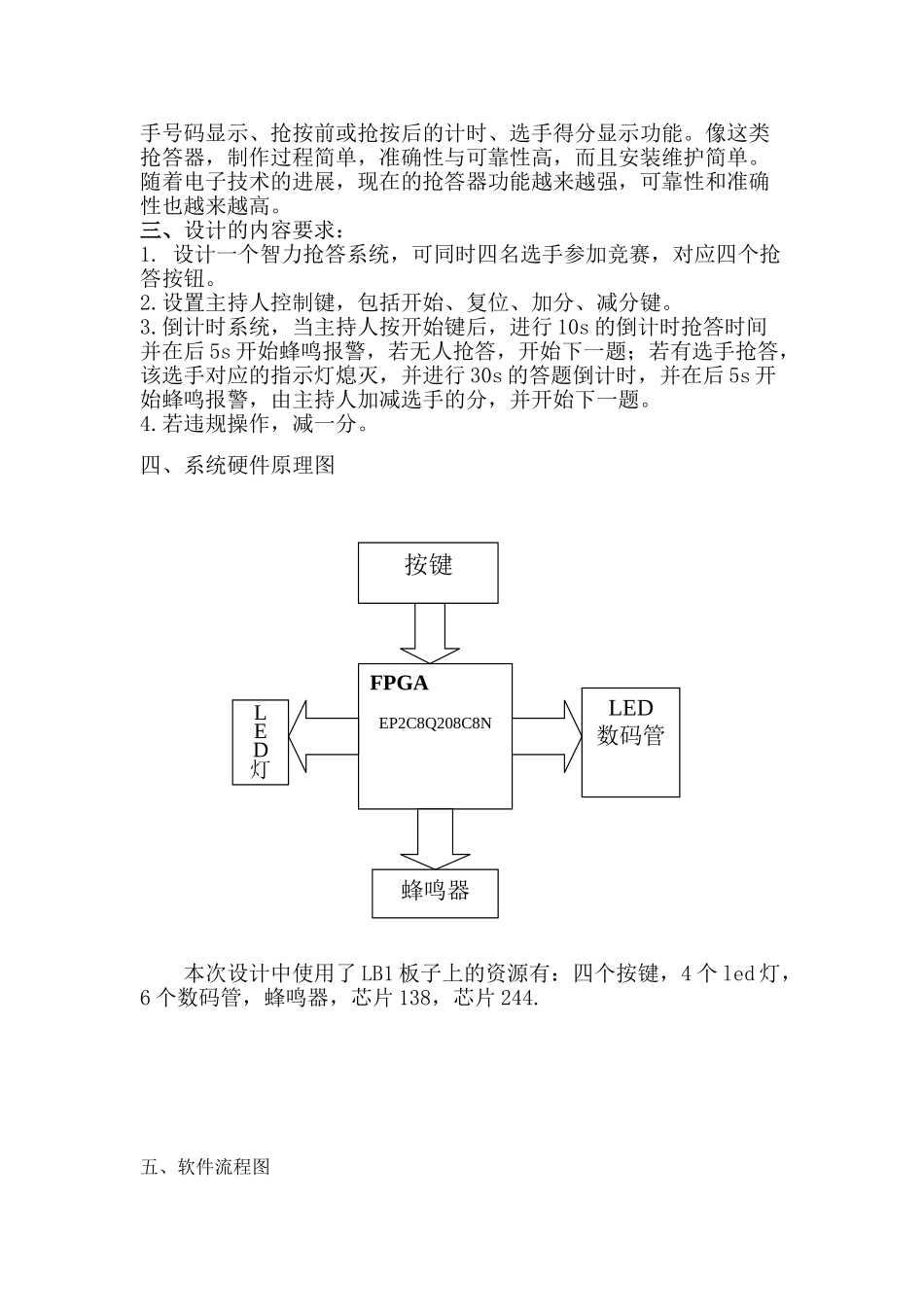

设计一个智力抢答系统,可同时四名选手参加竞赛,对应四个抢答按钮

设置主持人控制键,包括开始、复位、加分、减分键

倒计时系统,当主持人按开始键后,进行 10s 的倒计时抢答时间并在后 5s 开始蜂鸣报警,若无人抢答,开始下一题;若有选手抢答,该选手对应的指示灯熄灭,并进行 30s 的答题倒计时,并在后 5s 开始蜂鸣报警