第二章设x=2010×0

11011011,y=2100×(-0

10101100),求x+y

[解:]为了便于直观理解,假设两数均以补码表示,阶码采用双符号位,尾数采用单符号位,则它们的浮点表示分别为[x]浮=00010,0

11011011[y]浮=00100,1

01010100求阶差并对阶△E=Ex-Ey=[Ex]补+[-Ey]补=00010+11100=11110即△E为-2,x的阶码小,应使Mx右移两位,Ex加2,[x]浮=00100,0

00110110(11)其中(11)表示Mx右移2位后移出的最低两位数

00110110(11)+1

01010100────────────────1

10001010(11)规格化处理尾数运算结果的符号位与最高数值位同值,应执行左规处理,结果为1

00010101(10),阶码为00011

舍入处理采用0舍1入法处理,则有1

00010101+1────────────────1

00010110判溢出阶码符号位为00,不溢出,故得最终结果为x+y=2011×(-0

11101010)第三章存储器1、课本作业:P101:3,4题2

、已知cache/主存系统效率为85%,平均访问时间为60ns,cache比主存快4倍,求主存储器周期是多少

cache命中率是多少

解:因为:ta=tc/e所以:tc=ta×e=60×0

85=510ns(cache存取周期)tm=tc×r=510×4=204ns(主存存取周期)因为:e=1/[r+(1–r)H]所以:H=2

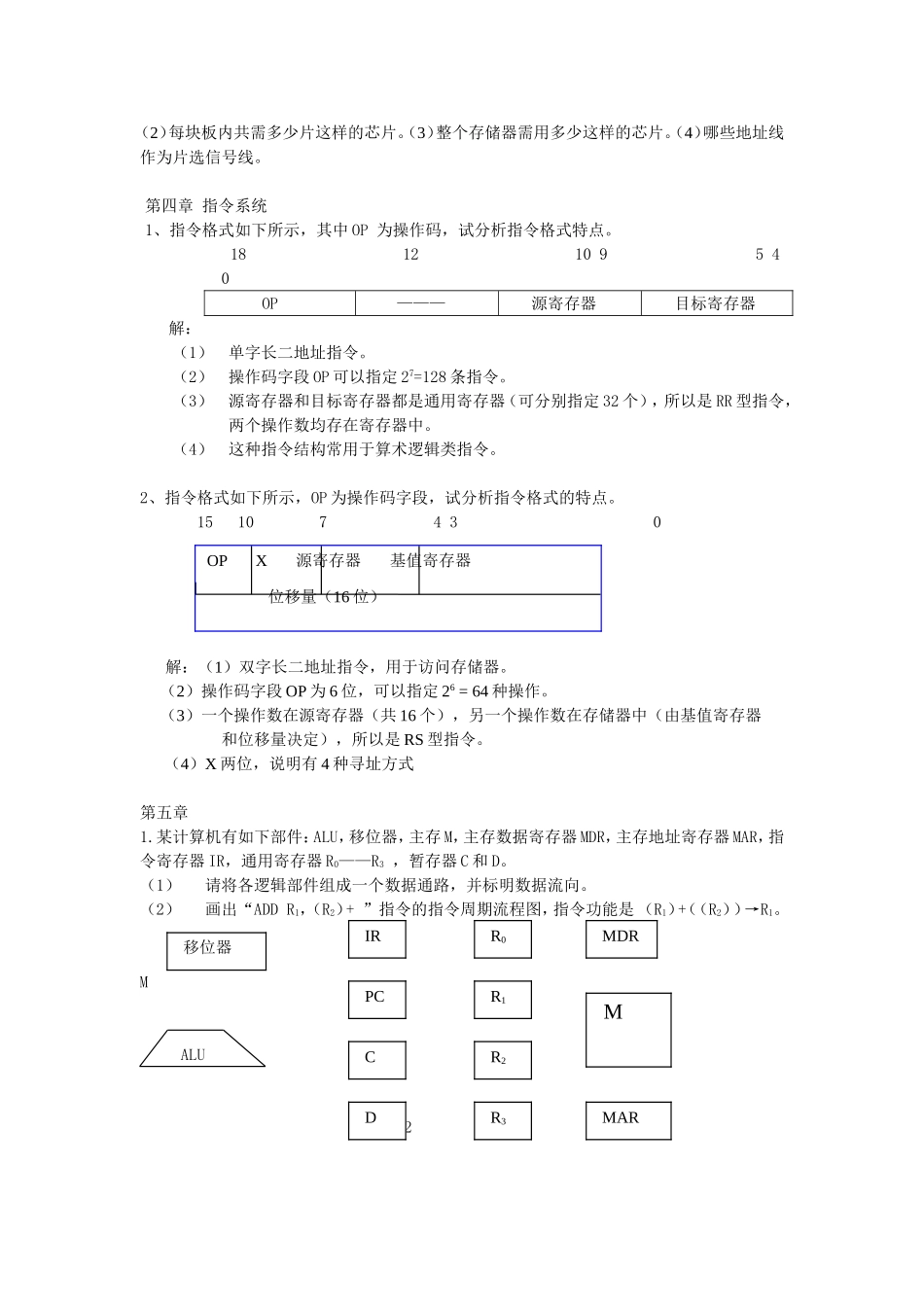

943、SRAM芯片有17位地址线和4位数据线

用这种芯片位32位字长的处理器构成1M×32位的存储器,并采用模块板结构

问(1)若每个模块板为256K×32位,需要几块板

(2)每块板内共需多少片这样的芯片

(3)整个存储器需用多少这样的芯