数字频率计 VH D L 程序与仿真一、功能:频率计

具有 4 位显示,能自动根据7位十进制计数得结果,自动选择有效数据得高 4 位进行动态显示

小数点表示就是千位,即 KHz

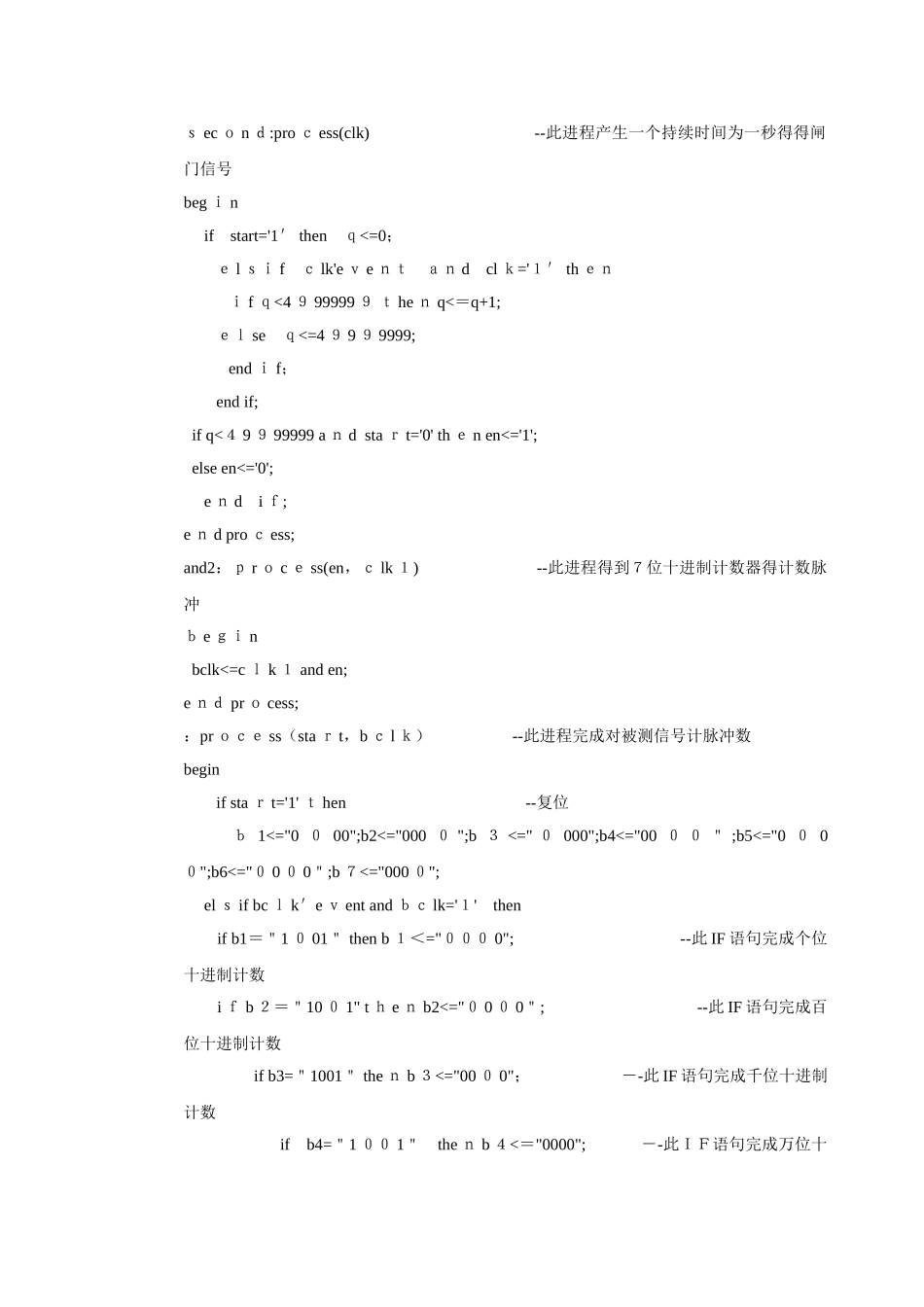

二、源程序及各模块与主要语句得功能l i b ra r y ie e e;use ie e e、st d_lo g i c_1 164、a l l;us e i e ee、s t d_l o g i c_un s ig n ed、a l l;e n ti ty pl j i s port ( start:in std_l ogi c; --复位信号 c l k :in s td_l ogic; --系统时钟 clk1:in std_lo g i c; --被测信号 yy 1:o ut st d_lo g i c_vector(7 dow n t o 0); --八段码 w1 :out st d_lo gi c_vec t or(3 d o w nt o 0)); --数码管位选信号end p lj;arch i t ectu r e behav o f PLj issignal b1,b2,b 3,b4,b5,b6,b7:std_lo g ic_vecto r(3 downto 0); --十进制计数器sig n al b c d:std_logic_vecto r(3 d ow n to 0); --B CD 码寄存器s i gnal q :i n teger r ange 0 t o 4 99 999 9 9; --秒分频系数 signal q q : integer rang e 0 t o 4 9 99 9 9; --动态扫描分频系数sig n a l e n,b c l k:std_logic; --使能信号,有效被测信号s igna l s s s : std_l ogic_vector