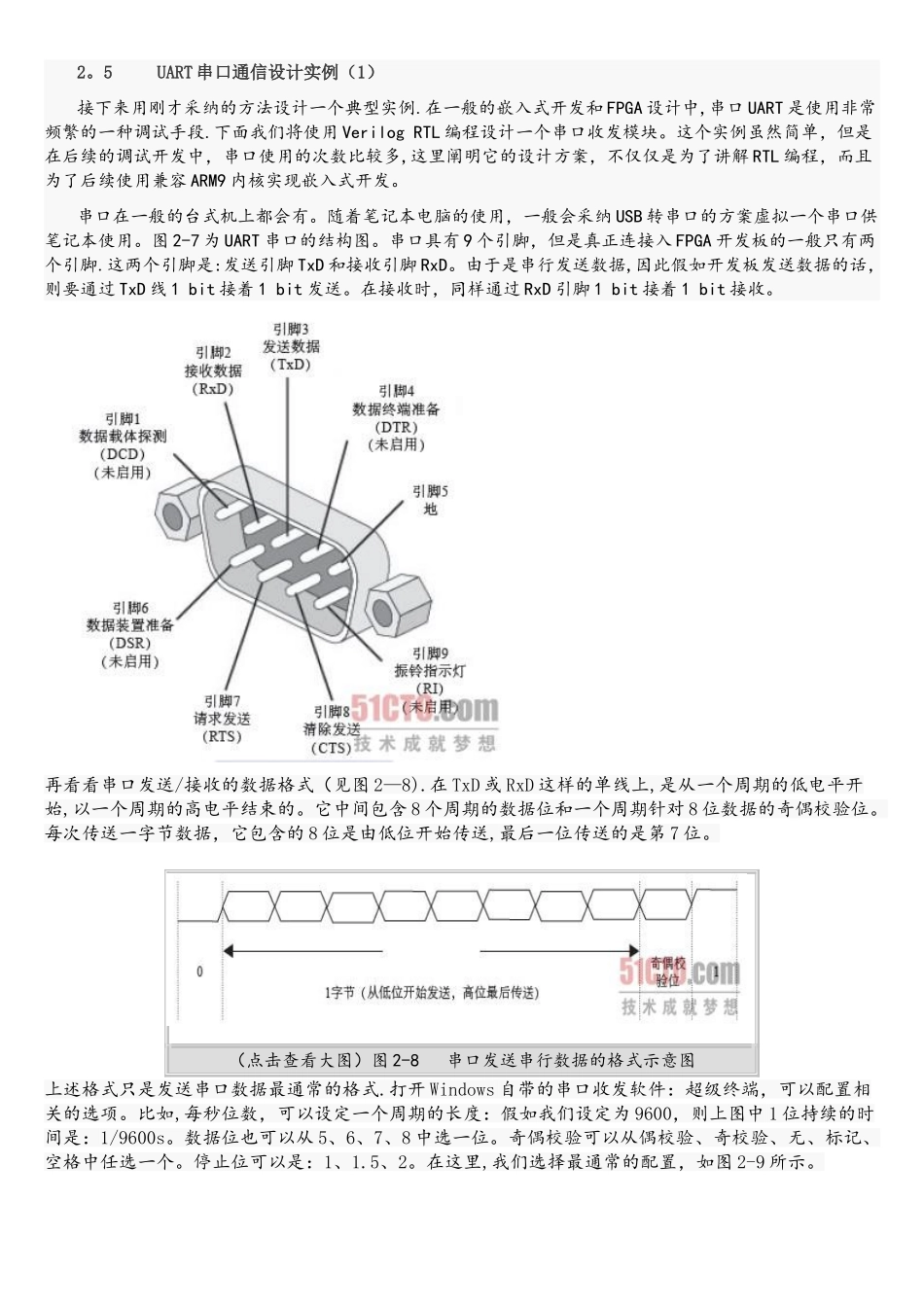

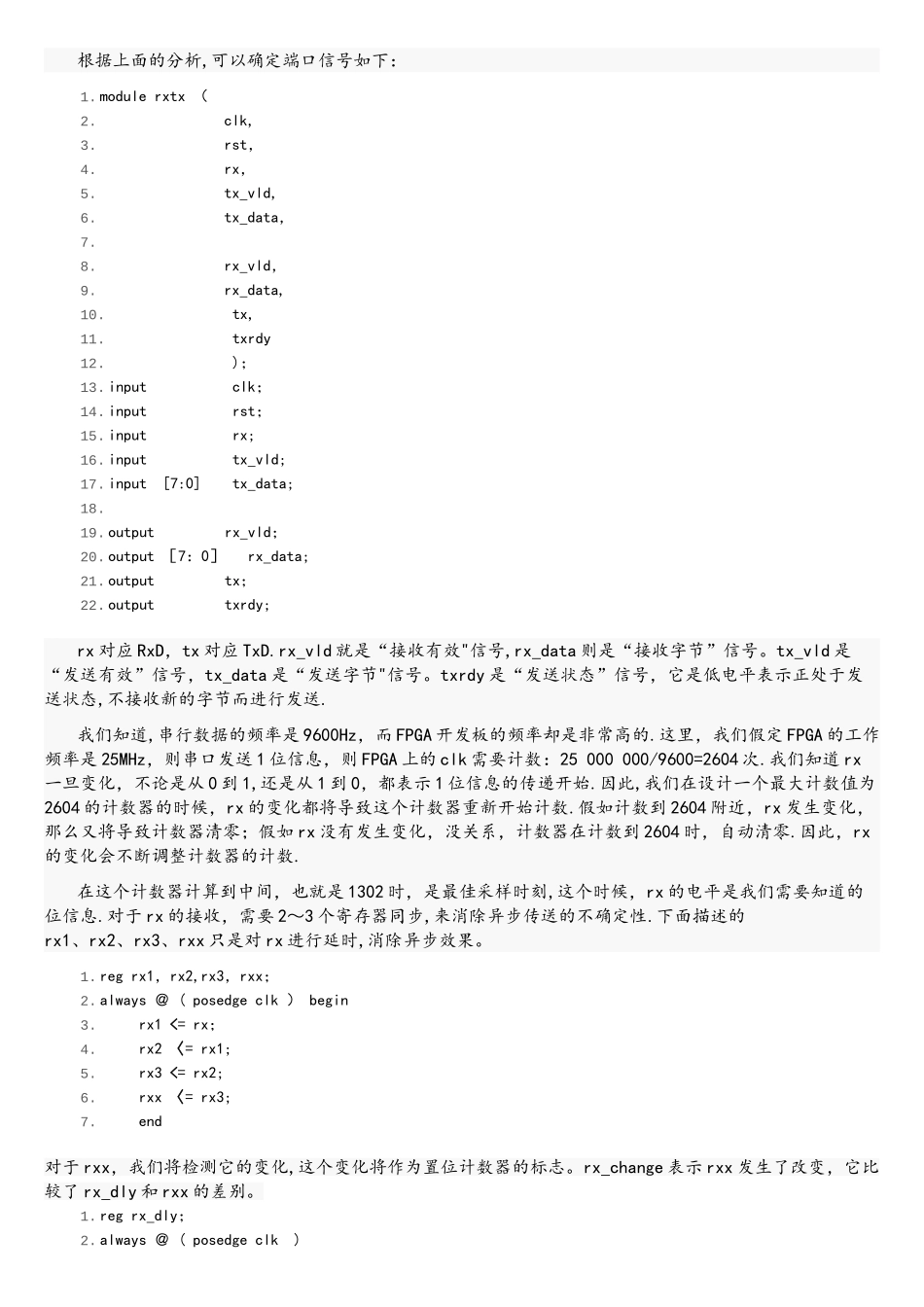

2。5 UART 串口通信设计实例(1)接下来用刚才采纳的方法设计一个典型实例.在一般的嵌入式开发和 FPGA 设计中,串口 UART 是使用非常频繁的一种调试手段.下面我们将使用 Verilog RTL 编程设计一个串口收发模块。这个实例虽然简单,但是在后续的调试开发中,串口使用的次数比较多,这里阐明它的设计方案,不仅仅是为了讲解 RTL 编程,而且为了后续使用兼容 ARM9 内核实现嵌入式开发。串口在一般的台式机上都会有。随着笔记本电脑的使用,一般会采纳 USB 转串口的方案虚拟一个串口供笔记本使用。图 2-7 为 UART 串口的结构图。串口具有 9 个引脚,但是真正连接入 FPGA 开发板的一般只有两个引脚.这两个引脚是:发送引脚 TxD 和接收引脚 RxD。由于是串行发送数据,因此假如开发板发送数据的话,则要通过 TxD 线 1 bit 接着 1 bit 发送。在接收时,同样通过 RxD 引脚 1 bit 接着 1 bit 接收。再看看串口发送/接收的数据格式(见图 2—8).在 TxD 或 RxD 这样的单线上,是从一个周期的低电平开始,以一个周期的高电平结束的。它中间包含 8 个周期的数据位和一个周期针对 8 位数据的奇偶校验位。每次传送一字节数据,它包含的 8 位是由低位开始传送,最后一位传送的是第 7 位。 (点击查看大图)图 2-8 串口发送串行数据的格式示意图上述格式只是发送串口数据最通常的格式.打开 Windows 自带的串口收发软件:超级终端,可以配置相关的选项。比如,每秒位数,可以设定一个周期的长度:假如我们设定为 9600,则上图中 1 位持续的时间是:1/9600s。数据位也可以从 5、6、7、8 中选一位。奇偶校验可以从偶校验、奇校验、无、标记、空格中任选一个。停止位可以是:1、1.5、2。在这里,我们选择最通常的配置,如图 2-9 所示。 这个设计有两个目的:一是从串口中接收数据,发送到输出端口。接收的时候是串行的,也就是一个接一个的;但是发送到输出端口时,我们希望是 8 位放在一起,成为并行状态(见图 2-10)。我们知道,串口中出现信号,是没有先兆的。假如出现了串行数据,则如何通知到输出端口呢?我们引入“接收有效”端口。“接收有效"端口在一般情况下都是低电平,一旦有数据到来时,它就变成高电平。下一个模块在得知“接收有效”信号为高电平常,它就明白:新到了一个字节的数据,放在“接收字节"端口里面。 图 2-10 串口接收和发送数据时进行串并转换的示意图二是发送数据到串口。发送...