实验一数字信号发生实验一、实验目的1.了解多种时钟信号的产生方法;2.了解PCM编码中的收、发帧同步信号的产生过程;3.掌握3级、4级、5级伪随机码的编码方法和伪随机码性质

二、实验仪器与设备1.THEXZ-2B型实验箱、数字信号发生模块;2.20MHz双踪示波器

三、实验原理时钟信号乃是数字通信各级电路的重要组成部分,在数字通信电路中,若没有时钟信号,则电路基本工作条件将得不到满足而无法工作

(一)电路组成时钟与伪码发生实验是供给PCM、PSK、FSK、HDB3等实验所需时钟和基带信号,由以下电路组成:1.内时钟信号源,图18-1

2.多级分频及脉冲编码调制系统收、发帧同步信号产生电路,图18-1

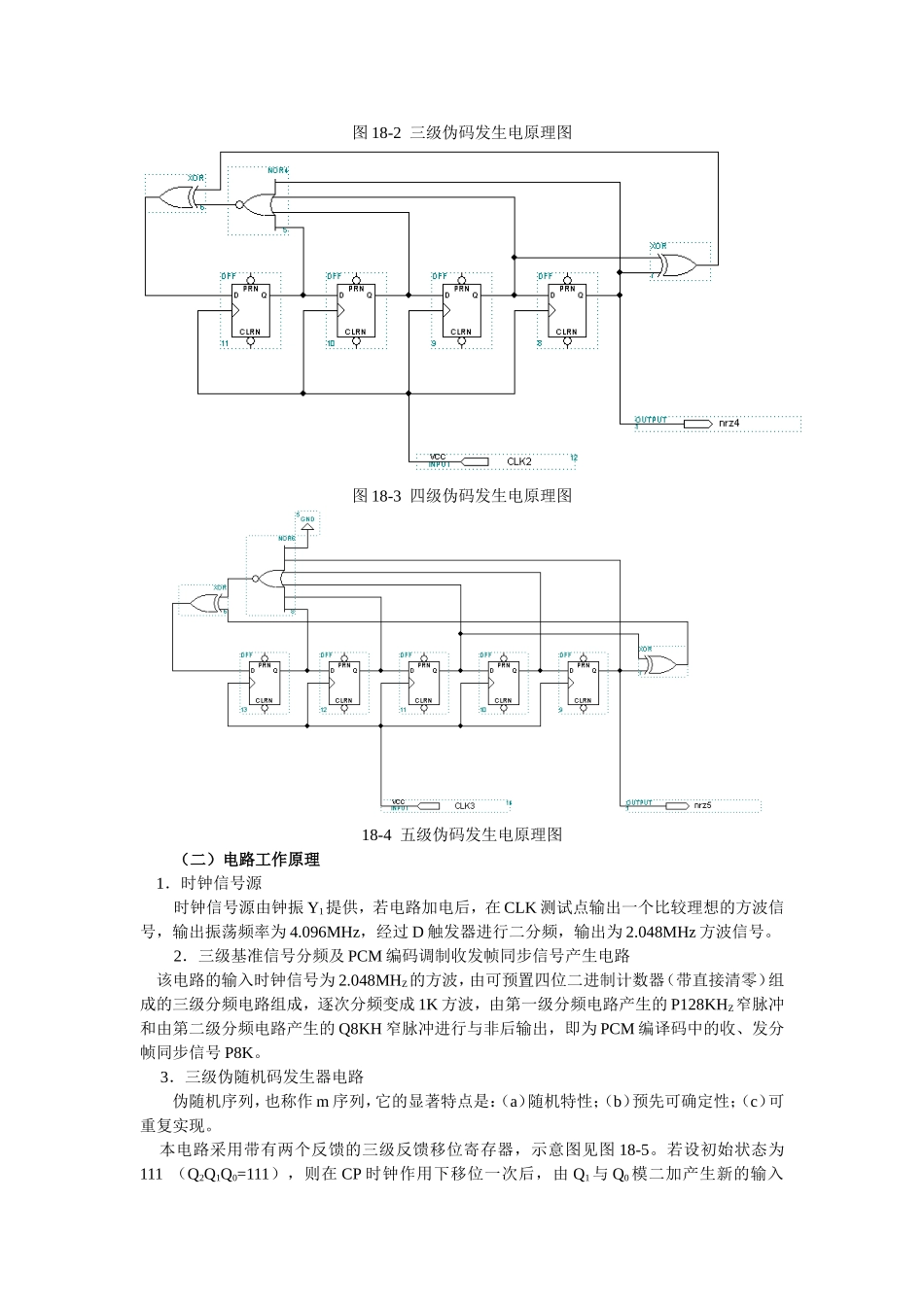

3.三级伪随机码发生电路,图18-2;4.四级伪随机码发生电路,图18-3;5.五级伪随机码发生电路,图18-4

图18-1时钟及多级分频及脉冲编码调制系统收、发帧同步信号产生电原理图图18-2三级伪码发生电原理图图18-3四级伪码发生电原理图18-4五级伪码发生电原理图(二)电路工作原理1.时钟信号源时钟信号源由钟振Y1提供,若电路加电后,在CLK测试点输出一个比较理想的方波信号,输出振荡频率为4

096MHz,经过D触发器进行二分频,输出为2

048MHz方波信号

2.三级基准信号分频及PCM编码调制收发帧同步信号产生电路该电路的输入时钟信号为2

048MHZ的方波,由可预置四位二进制计数器(带直接清零)组成的三级分频电路组成,逐次分频变成1K方波,由第一级分频电路产生的P128KHZ窄脉冲和由第二级分频电路产生的Q8KH窄脉冲进行与非后输出,即为PCM编译码中的收、发分帧同步信号P8K

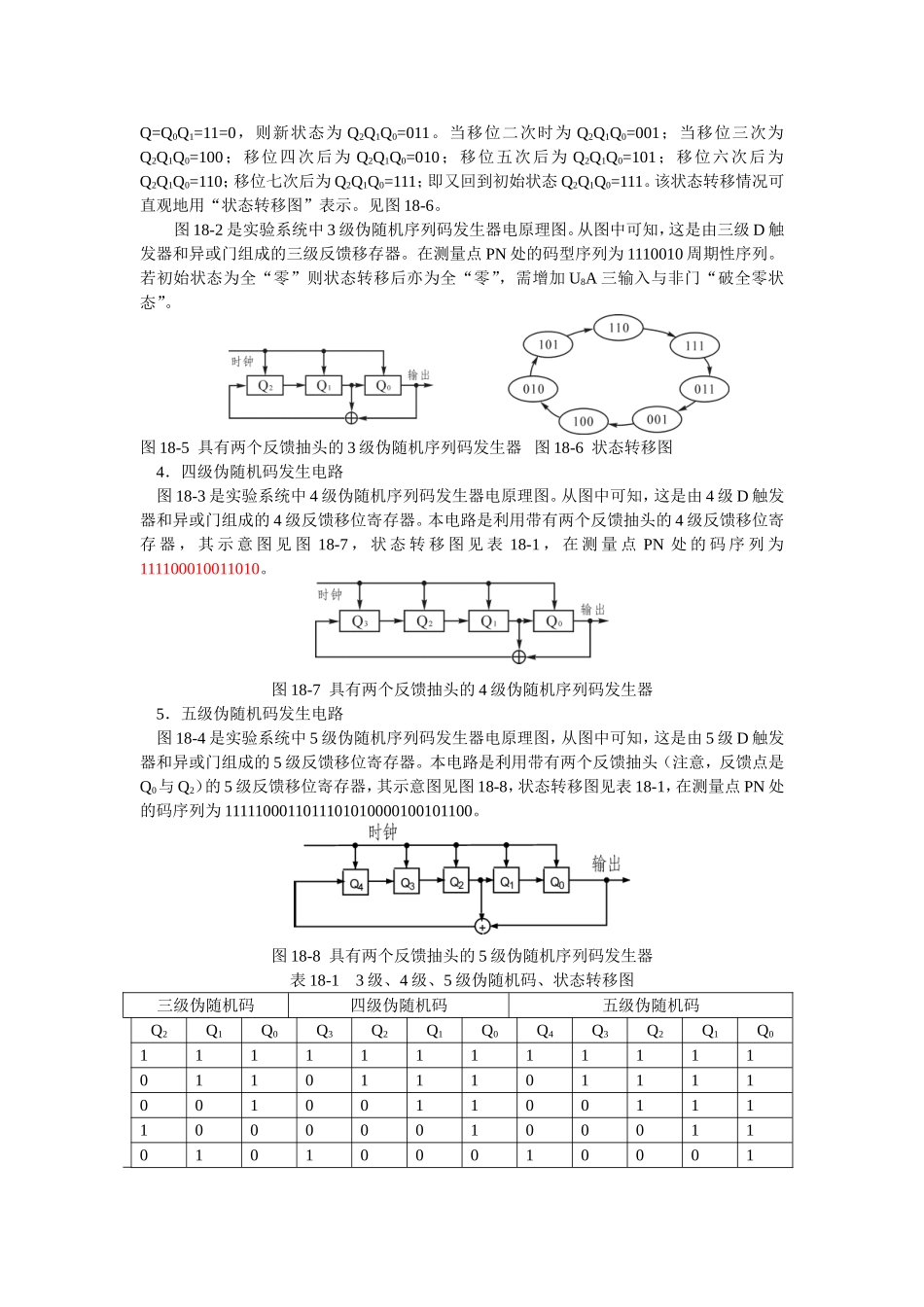

3.三级伪随机码发生器电路伪随机序列,也称作m序列,它的显著特点是:(a)随机特性;(b)预先可确定性;(c)可重复实现

本电路采用带有两个反馈的三级反馈移位寄存器,示意图见图18-5