基于VHDL的数字闹钟设计摘要:随着EDA技术的发展和应用领域的扩大与深入,EDA技术在电子信息、通信、自动控制及计算机应用领域的重要性日益突出

EDA技术就是依赖功能强大的计算机,在EDA工具软件平台上,对以硬件描述语言VHDL为系统逻辑描述手段完成的设计文件,自动地完成逻辑优化和仿真测试,直至实现既定的电子线路系统功能

本文介绍了基于VHDL硬件描述语言设计的多功能数字闹钟的思路和技巧

在Quartus11开发环境中编译和仿真了所设计的程序,并逐一调试验证程序的运行状况

仿真和验证的结果表明,该设计方法切实可行,该数字闹钟可以实现调时定时闹钟播放音乐功能具有一定的实际应用性

关键字:闹钟FPGAVHDLQuartusII一、电子钟相关功能描述如下:(1)计时功能:这是本计时器设计的基本功能,可进行时、分、秒计时,并显示

(2)闹钟功能:如果当前时间与设置的闹钟时间相同,则扬声器发出一段音乐,并维持一分钟

(3)调时调分调闹钟功能:当需要校时或者要重新设置闹钟的时间时,可通过实验箱上的按键控制

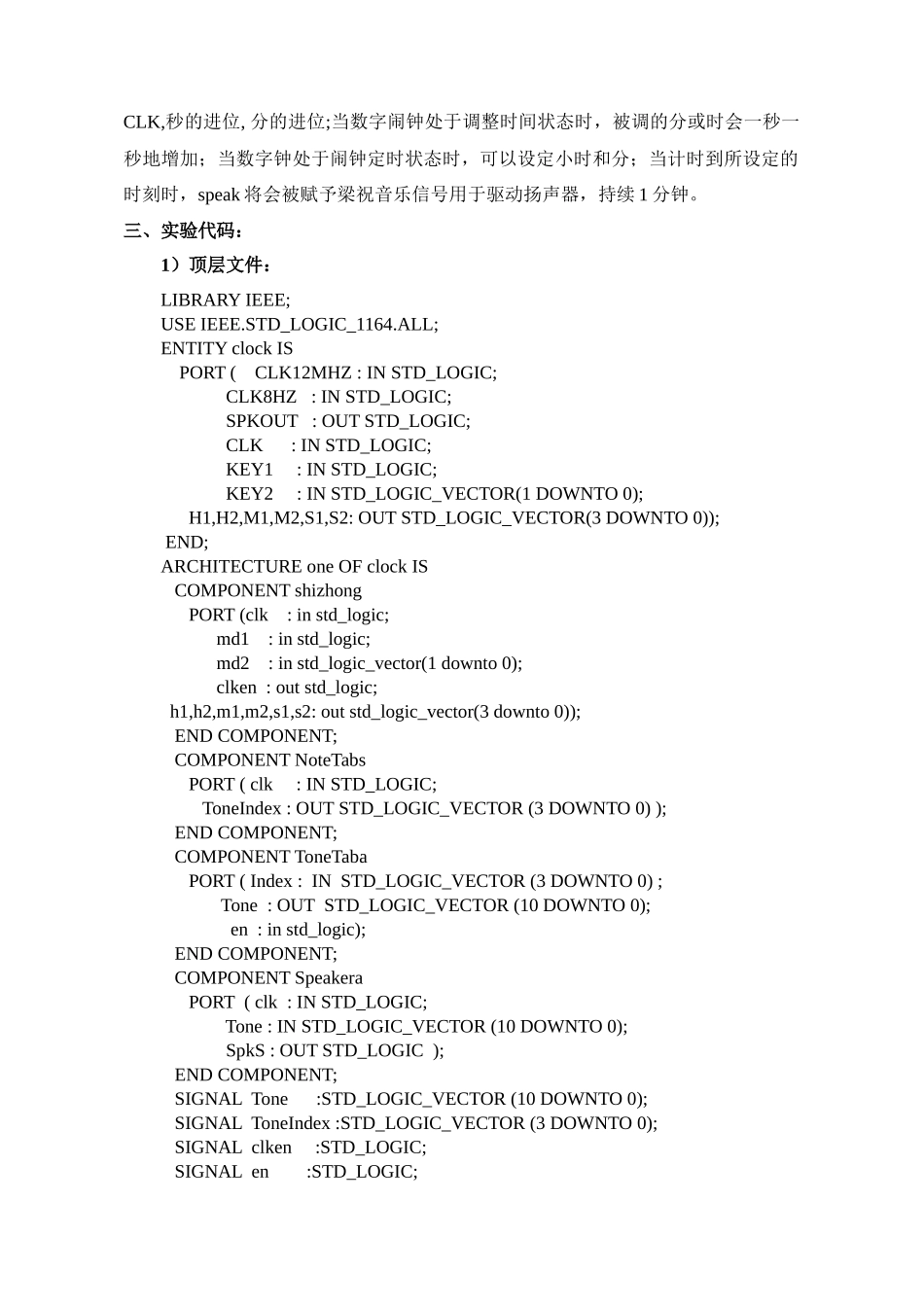

二、设计原理:数字闹钟电路的基本结构由两个60进制计数器和一个24进制计数器组成,分别对秒、分、小时进行计时,当计时到23时59分59秒时,再来一个计数脉冲,则计数器清零,重新开始计时

秒计数器的计数时钟CLK为1Hz的标准信号

当数字闹钟处于计时状态时,秒计数器的进位输出信号作为分钟计数器的计数信号,分钟计数器的进位输出信号又作为小时计数器的计数信号时、分、秒的计时结果通过6个数码管来动态显示

数字闹钟除了能够正常计时外,还应能够对时间进行调整

因此,通过模式选择信号KEY1、KEY2控制数字钟的工作状态,即控制数字钟,使其分别工作于正常计时,调整分、时和设定闹钟分、时5个状态

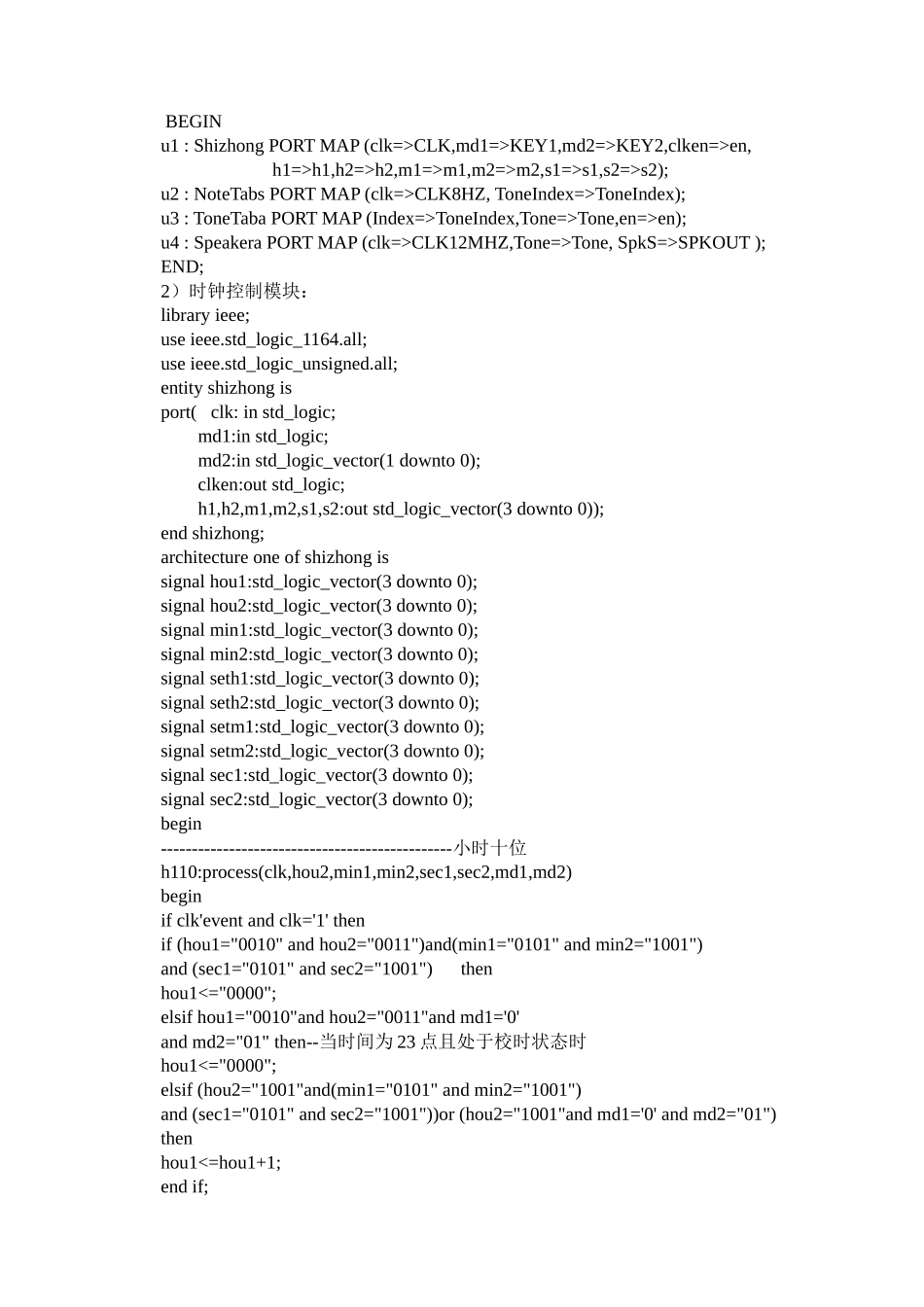

当数字闹钟处于计时状态时,3个计数器允许计数,且秒、分、时计数器的计数时钟信号分别为CLK,秒的进位,