电子科技大学UNIVERSITYOFELECTRONICSCIENCEANDTECHNOLOGYOFCHINA数字逻辑设计实验报告实验题目:4bit模9加法器学生姓名:指导老师:一、实验内容设计一个4bit模9加法器

输入为两个4bit的二进制数,输出为两数相加后模9的结果

其数学表达式为:y=(x1+x2)mod9

二、实验要求1、功能性要求:能够实现4bit无符号数的模9加法运算,即输入两个4比特数据时能够正确输出其相加并模9运算结果

2、算法要求:模加法器有多种算法,可采用任意算法进行设计

3、设计性要求:采用全加器、半加器和基本门结构化描述

能够编写TestBench文件,并利用Modelsim进行仿真

在Modelsim仿真正确的基础上,能够生成bit文件并上板验证其正确性

4、基本上板要求:在上板实验时,输入的两个4bit数采用拨码开关输入,输出采用LED灯进行显示

三、设计思路1、整体思路:为了实现4bit无符号数的模9加法运算,可以先将两个4bit的加数a和b先分别模9,相加之后再模9得到最终结果

2、模9器:先找出读入的5bit数与模9后的4bit数之间的关系,画出卡诺图,再根据卡诺图得出其相应的逻辑表达式即可

设读入的5bit数为carry、a、b、c、d,模9后得到的4bit数为w、x、y、z

则化简后得到的逻辑表达式分别为:w=carry’ab’c’d’,x=carry’bc+carry’a’b+carry’bd+carrya’b’c’d’,y=carry’a’c+carry’cd+carry’abc’d’+carrya’b’c’d’,z=carry’a’d+carry’acd’+carry’abd’+carrya’b’c’d’

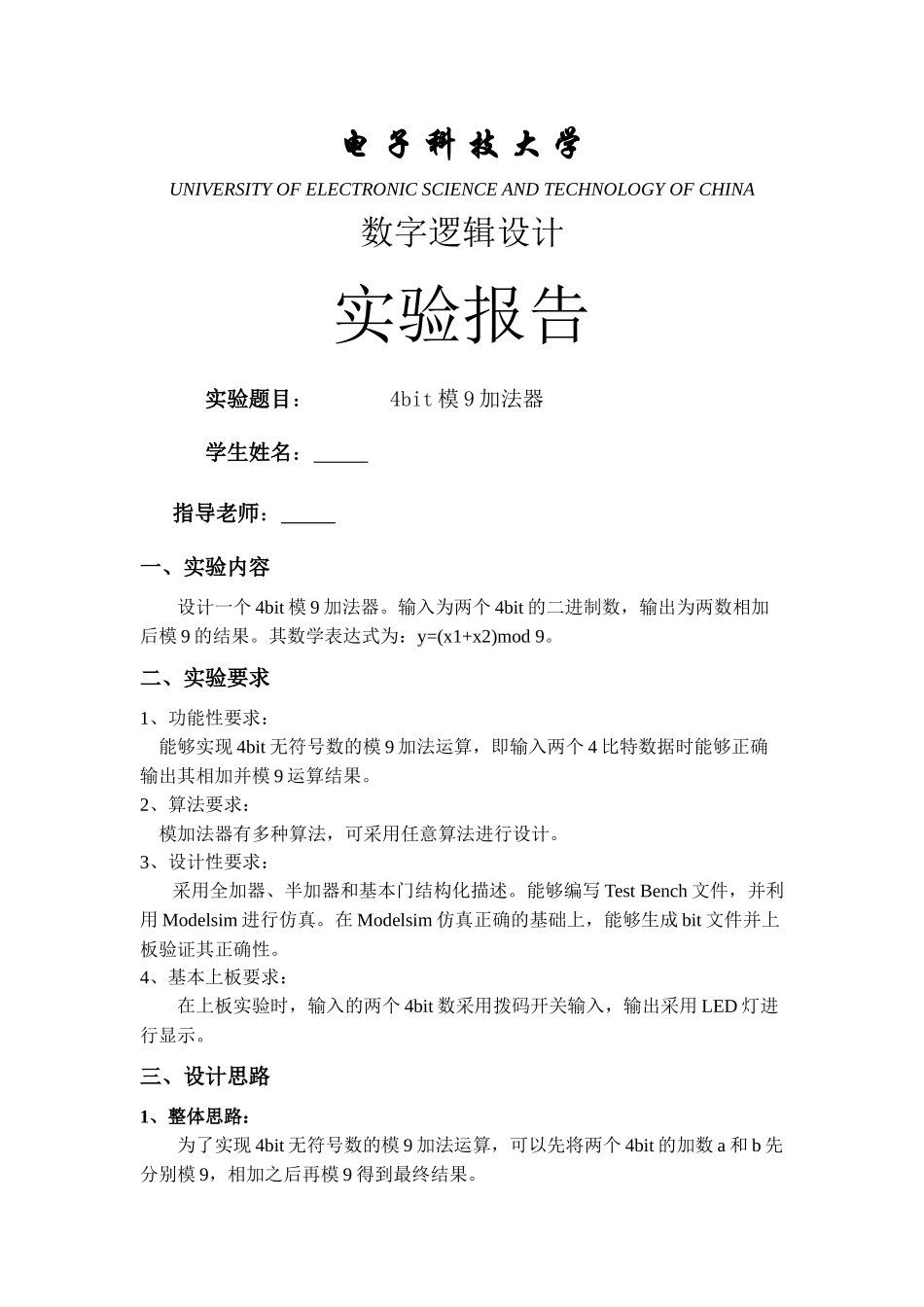

3、全加器:全加器可以实现两个1bit数a、b和进位输入cin的相加,其真值表如下所示:这里全加器由半加器和或门构成,其原