32位浮点加法器设计摘要:浮点数具有数值范围大,表示格式不受限制的特点,因此浮点数的应用是非常广泛的

浮点数加法运算比较复杂,算法很多,但是为了提高运算速度,大部分均是基于流水线的设计结构

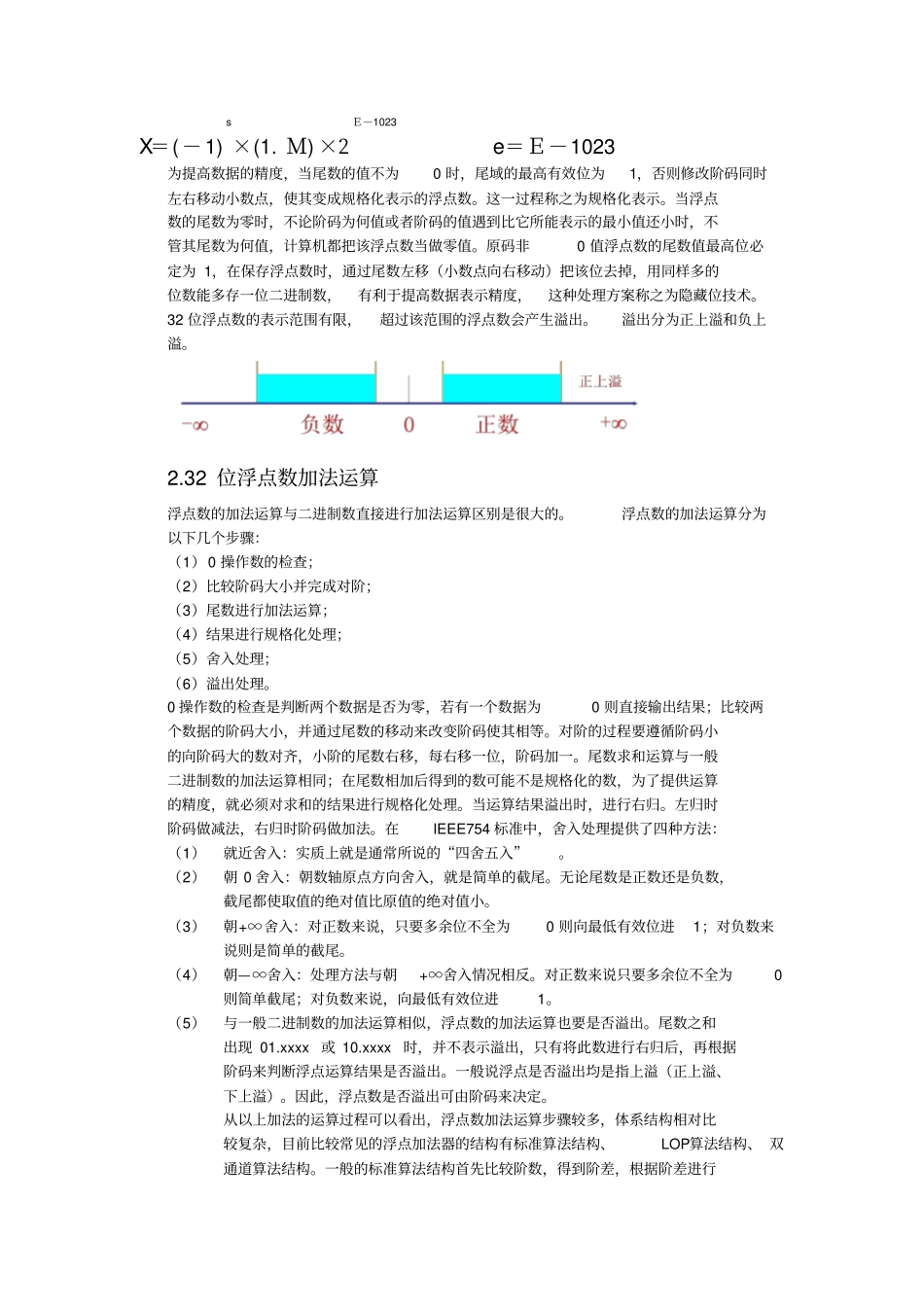

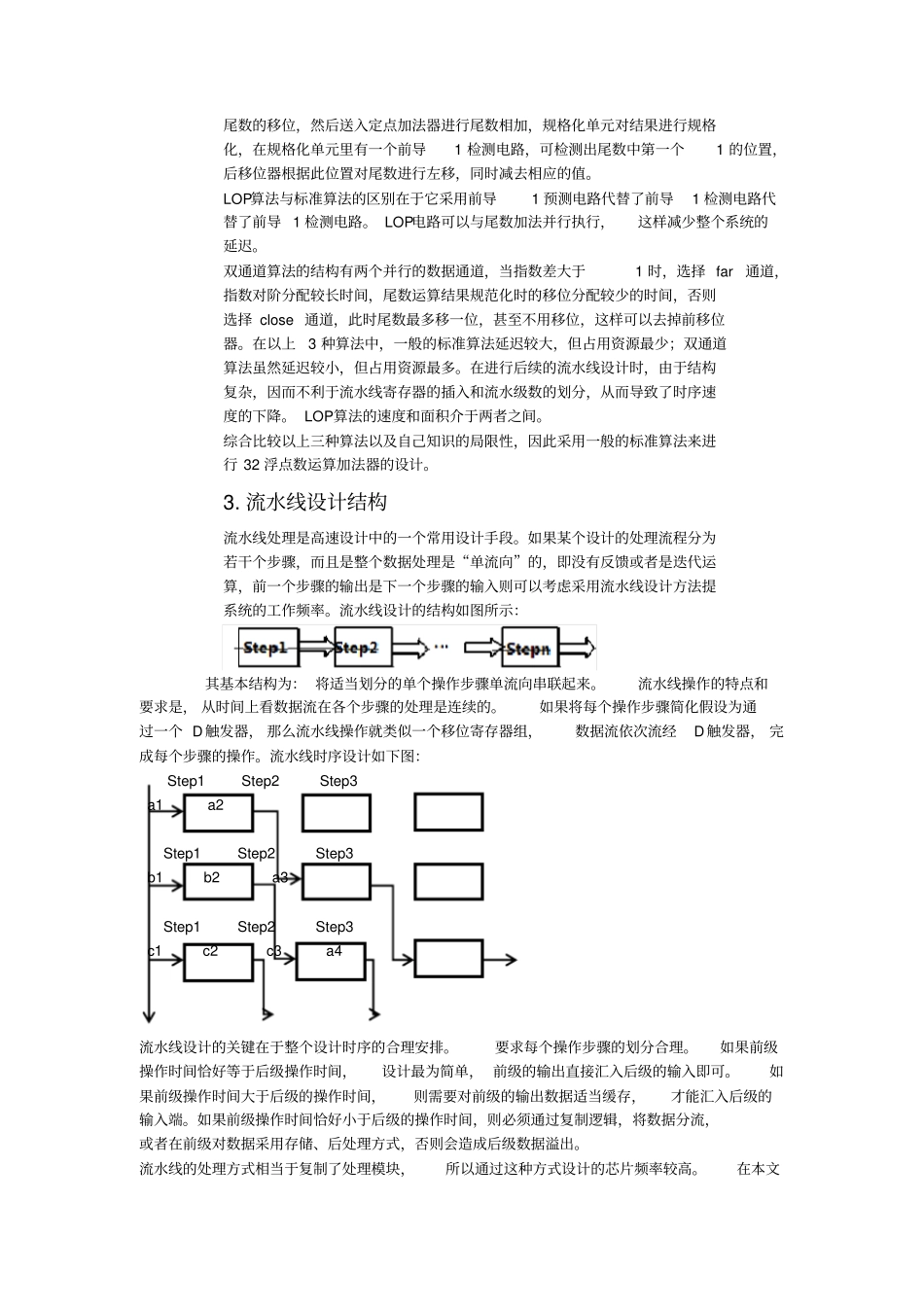

本文介绍了基于IEE754标准的用Verilog语言设计的32位浮点加法器,能够实现32位浮点数的加法运算

虽然未采用流水线的设计结构但是仍然对流水线结构做了比较详细的介绍

关键字:浮点数,流水线,32位浮点数加法运算,Verilog语言设计32-bitfloatingpointadderdesignCaoChi,ShenJia-qi,ZhengYun-jia(SchoolofMechatronicEngineeringandAutomation,ShanghaiUniversity,Shanghai,China)Abstract://沈佳琪搞定Keywords:float;Assemblyline;32-bitfloating-pointadder浮点数的应用非常广泛,无论是在计算机还是微处理器中都离不开浮点数

但是浮点数的加法运算规则比较复杂不易理解掌握,而且按照传统的运算方法,运算速度较慢

因此,浮点加法器的设计采用了流水线的设计方法

32位浮点数运算的摄入处理采用了IEE754标准的“0舍1入”法

浮点数的介绍在处理器中,数据不仅有符号,而且经常含有小数,即既有整数部分又有小数部分

根据小数点位置是否固定,数的表示方法分为定点表示和浮点表示

浮点数就是用浮点表示法表示的实数

浮点数扩大了数的表示范围和精度

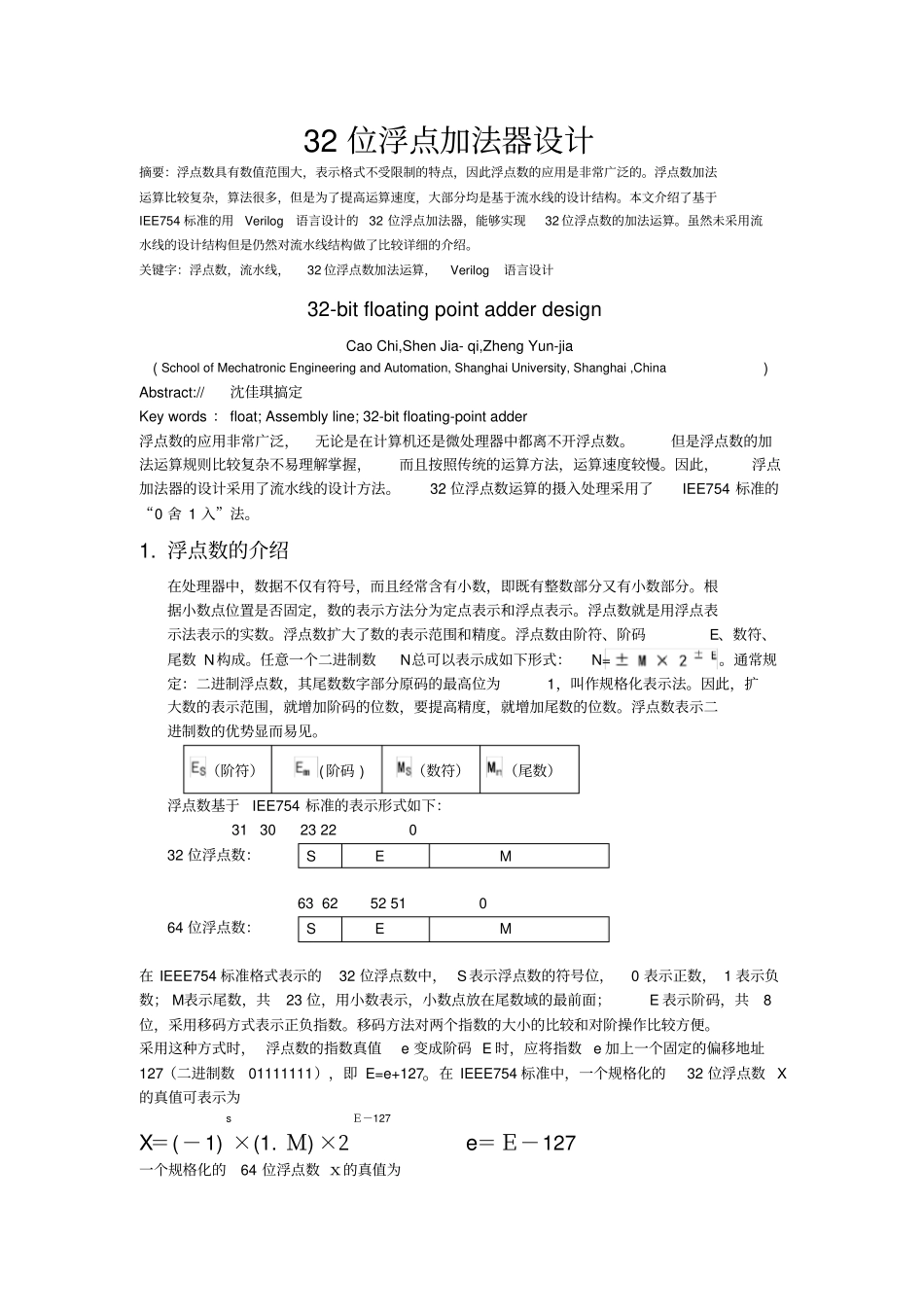

浮点数由阶符、阶码E、数符、尾数N构成

任意一个二进制数N总可以表示成如下形式:N=

通常规定:二进制浮点数,其尾数数字部分原码的最高位为1,叫作规格化表示法

因此,扩大数的表示范围,就增加阶码的位数,要提高精度,就增加尾数的位数

浮点数表示二进制数的优势显而易见