实验八计数器一、实验目的1.熟悉由集成触发器构成的计数器电路及其工作原理

2.熟悉掌握常用中规模集成电路计数器及其应用方法

二、实验原理和电路所谓计数,就是统计脉冲的个数,计数器就是实现“计数”操作的时序逻辑电路

计数器的应用十分广泛,不仅用来计数,也可用作分频、定时等

计数器种类繁多

根据计数体制的不同,计数器可分成二进制(即2”进制)计数器和非二进制计数器两大类

在非二进制计数器中,最常用的是十进制计数器,其它的一般称为任意进制计数器

根据计数器的增减趋势不同,计数器可分为加法计数器—随着计数脉冲的输入而递增计数的;减法计数器—随着计数脉冲的输入而递减的;可逆计数器—既可递增,也可递减的

根据计数脉冲引入方式不同,计数器又可分为同步计数器—计数脉冲直接加到所有触发器的时钟脉冲(CP)输入端;异步计数器—计数脉冲不是直接加到所有触发器的时钟脉冲(CP)输入端

异步二进制加法计数器异步二进制加法计数器是比较简单的

图是由4个JK(选用双JK74LS112)触发器构成的4位二进制(十六进制)异步加法计数器,图和(c)分别为其状态图和波形图

对于所得状态图和波形图可以这样理解:触发器FFO(最低位)在每个计数沿(CP)的下降沿(1→0)翻转,触发器FF1的CP端接FF0的Q0端,因而当FFO(QO)由1→0时,FF1翻转

类似地,当FF1(Q1)由1→0时,FF2翻转,FF2(Q2)由1→0时,FF3翻转

4位二进制异步加法计数器从起始态0000到1111共十六个状态,因此,它是十六进制加法计数器,也称模16加法计数器(模M=16)

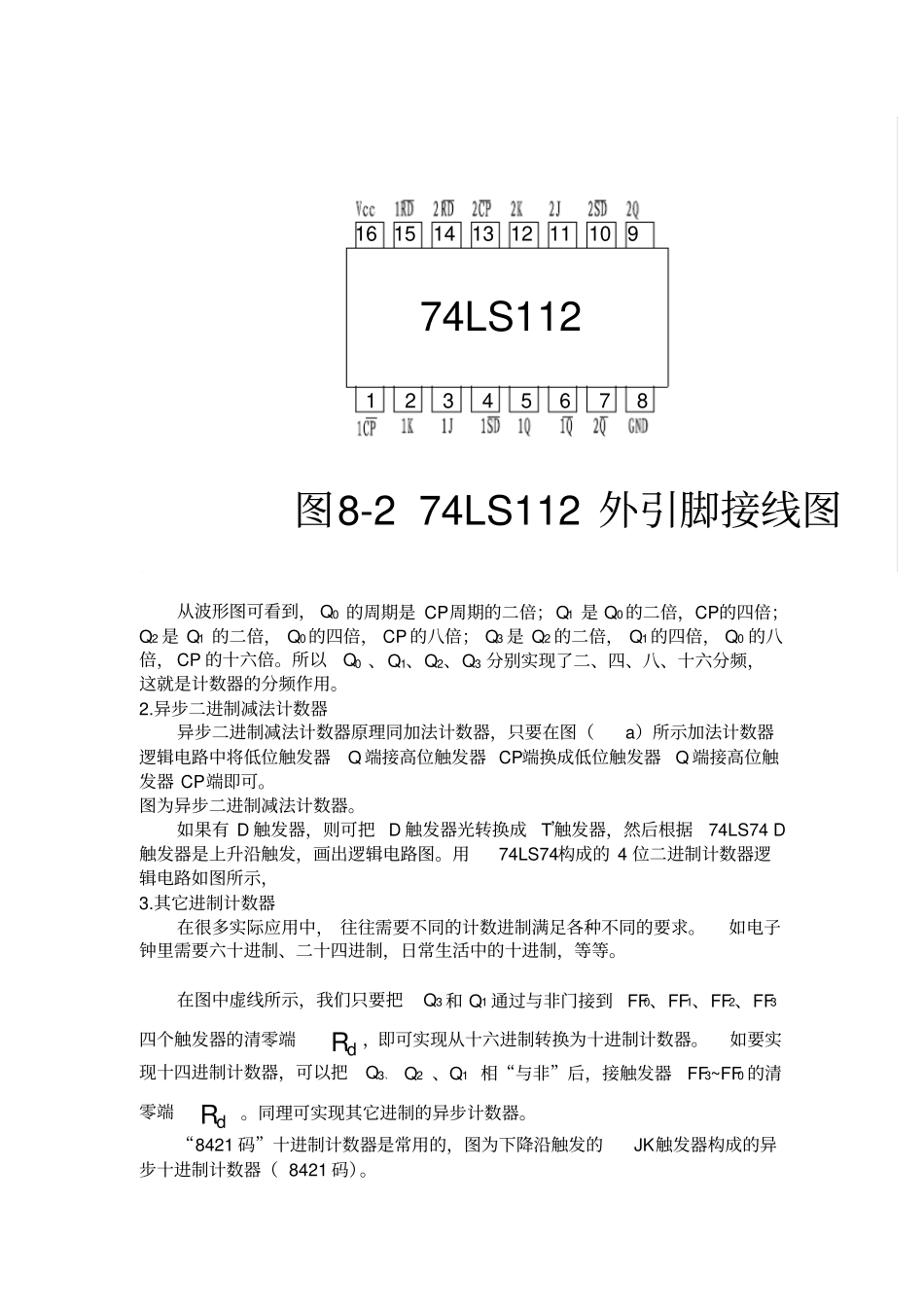

74LS11212345161514131267811109图8-274LS112外引脚接线图从波形图可看到,Q0的周期是CP周期的二倍;Q1是Q0的二倍,CP的四倍;Q2是Q1的二倍,Q0的四倍,CP的八倍;Q3是Q2的二倍,Q1的四倍,Q0