第1页共28页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第1页共28页74ls00是常用的2输入四与非门集成电路,他的作用很简单顾名思义就是实现一个与非门

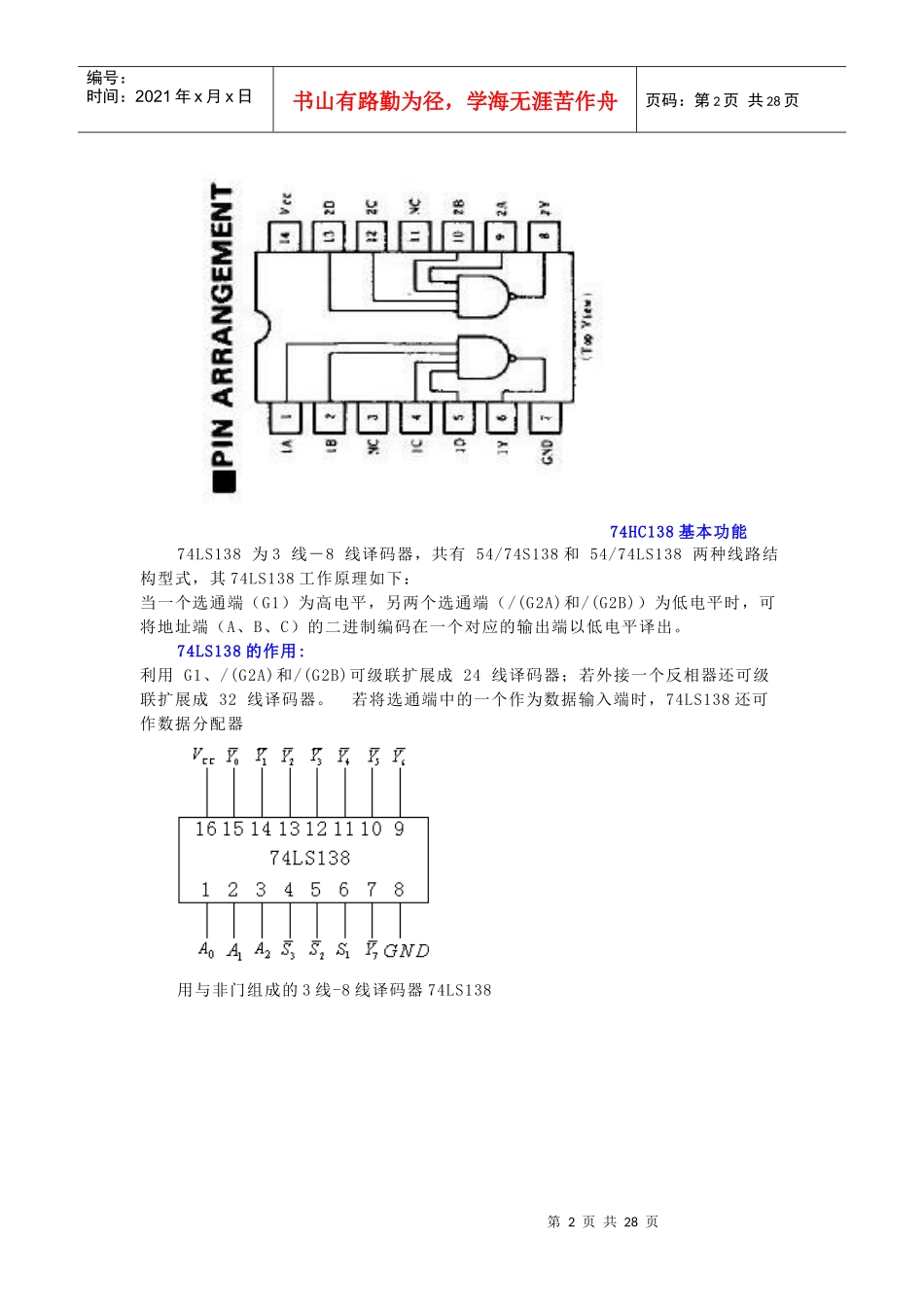

Vcc4B4A4Y3B3A3Y┌┴—┴—┴—┴—┴—┴—┴┐__│141312111098│Y=AB)│2输入四正与非门74LS00│1234567│└┬—┬—┬—┬—┬—┬—┬┘1A1B1Y2A2B2YGND74LS00真值表:A=1B=1Y=0A=0B=1Y=1A=1B=0Y=1A=0B=0Y=1第2页共28页第1页共28页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第2页共28页74HC138基本功能74LS138为3线-8线译码器,共有54/74S138和54/74LS138两种线路结构型式,其74LS138工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出

74LS138的作用:利用G1、/(G2A)和/(G2B)可级联扩展成24线译码器;若外接一个反相器还可级联扩展成32线译码器

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS138第3页共28页第2页共28页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第3页共28页图74ls138译码器内部电路3线-8线译码器74LS138的功能表备注:这里的输入端的三个A0~1有的原理图中也用ABC表示(如74H138

pdf中所示,试用于普中科技的HC-6800V2

2单片机开发板)

74LS138逻辑图无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平