时序电路逻辑设计实验人:周铮班级:中法1202班学号:U201215676一实验目的1

掌握用SSI实现简单组合逻辑电路的方法

掌握简单数字电路的安装与测试技术

熟悉使用VerilogHDL描述组合逻辑电路的方法,以及EDA仿真技术

二实验器件计算机,可编程实验板三实验内容十进制加减可逆计数器设计功能要求:拨码开关键SW1为自动可逆加减功能键,当SW1为HIGH时,计数器实现自动可逆模十加减计数功能,即4个七段数码管上几乎同步显示0—1—2—3—4—⋯9—8—7—⋯0—1⋯的模十自动可逆加减计数结果;当SW1为LOW时,计数器按拨码开关键SW0的选择分别执行加减计数功能

即当SW0为HIGH时,计数器实现模十加计数功能,即4个七段数码管上几乎同步显示0—1—2—3—4—⋯9——0—1⋯的模十加计数结果;当SW0为LOW时,计数器实现模十减计数功能,即4个七段数码管上几乎同步显示9—8—7—⋯—1—0—⋯9—8—7⋯的模十减计数结果

四实验设计1

原理设计脉冲发生电路采用555定时器组成的多谐振荡器振荡产生周期为1s的矩形脉冲,从而为计数器提供触发信号

其中,可以通过R1,R2,C来控制充放电的时间

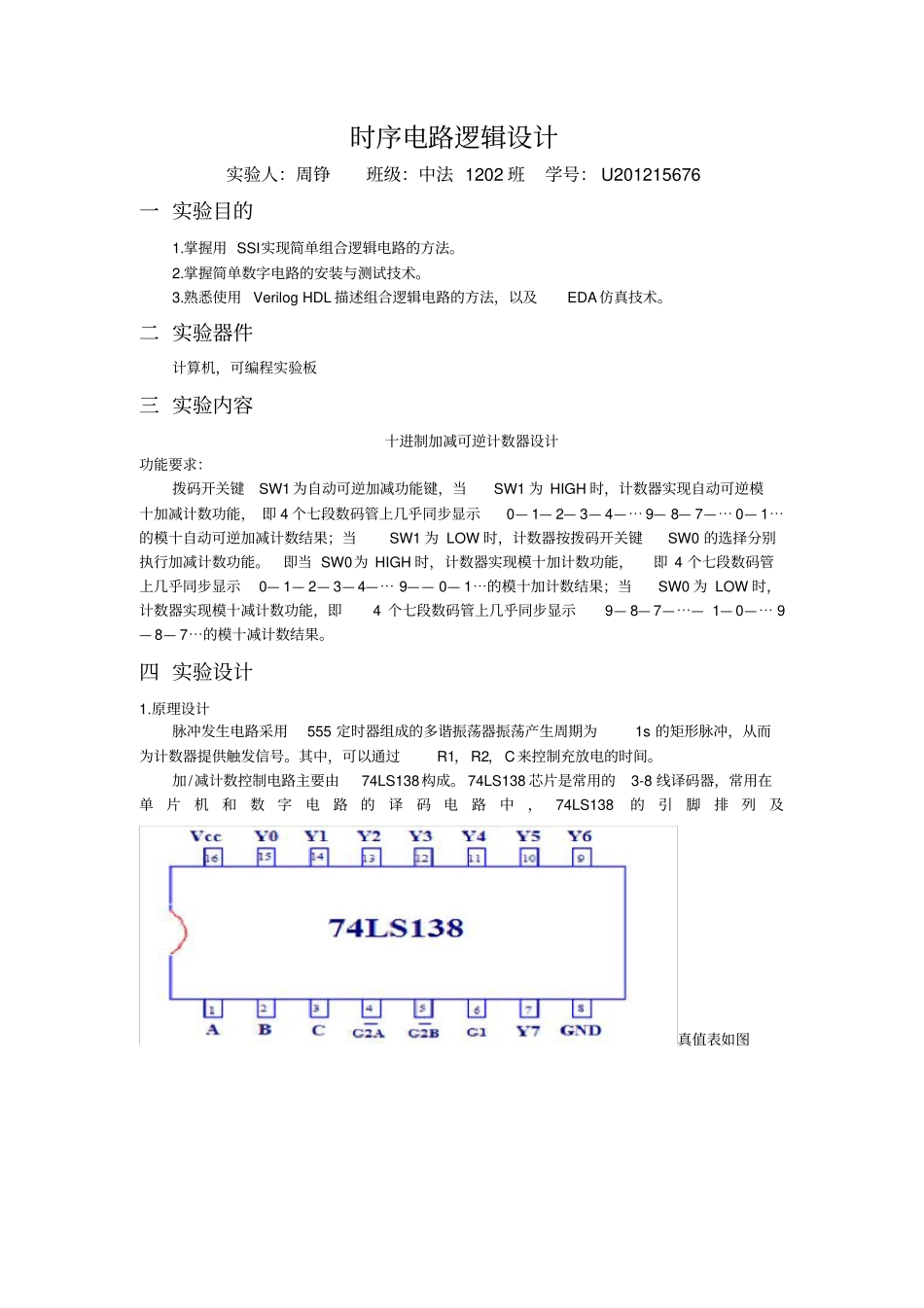

加/减计数控制电路主要由74LS138构成

74LS138芯片是常用的3-8线译码器,常用在单片机和数字电路的译码电路中,74LS138的引脚排列及真值表如图计数单元电路主要由十进制计数器74LS192构成

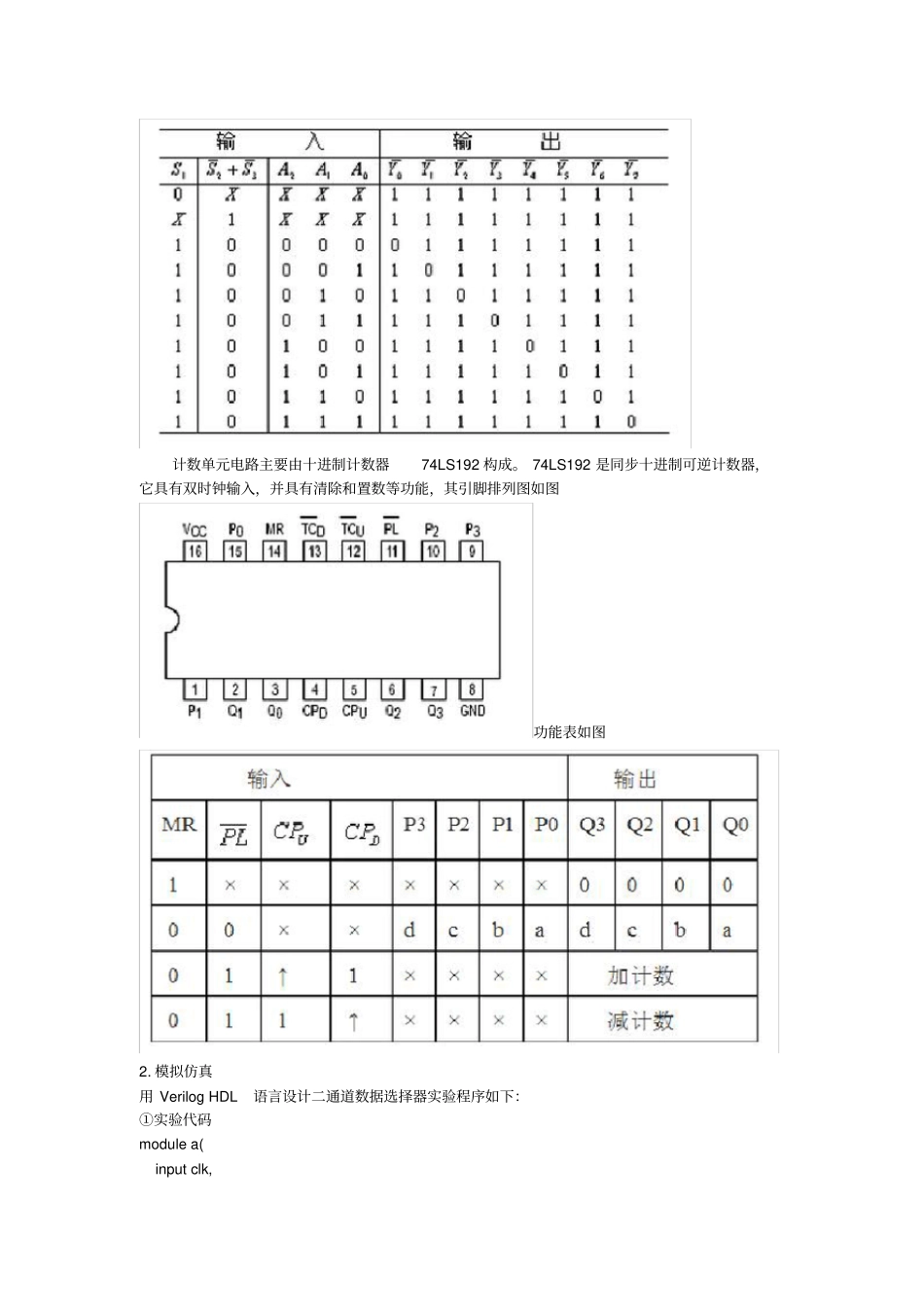

74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列图如图功能表如图2

模拟仿真用VerilogHDL语言设计二通道数据选择器实验程序如下:①实验代码modulea(inputclk,inputSW1,inputSW0,inputclear,inputreset,outputreg[3:0]s1_reg,outputreg[6:0