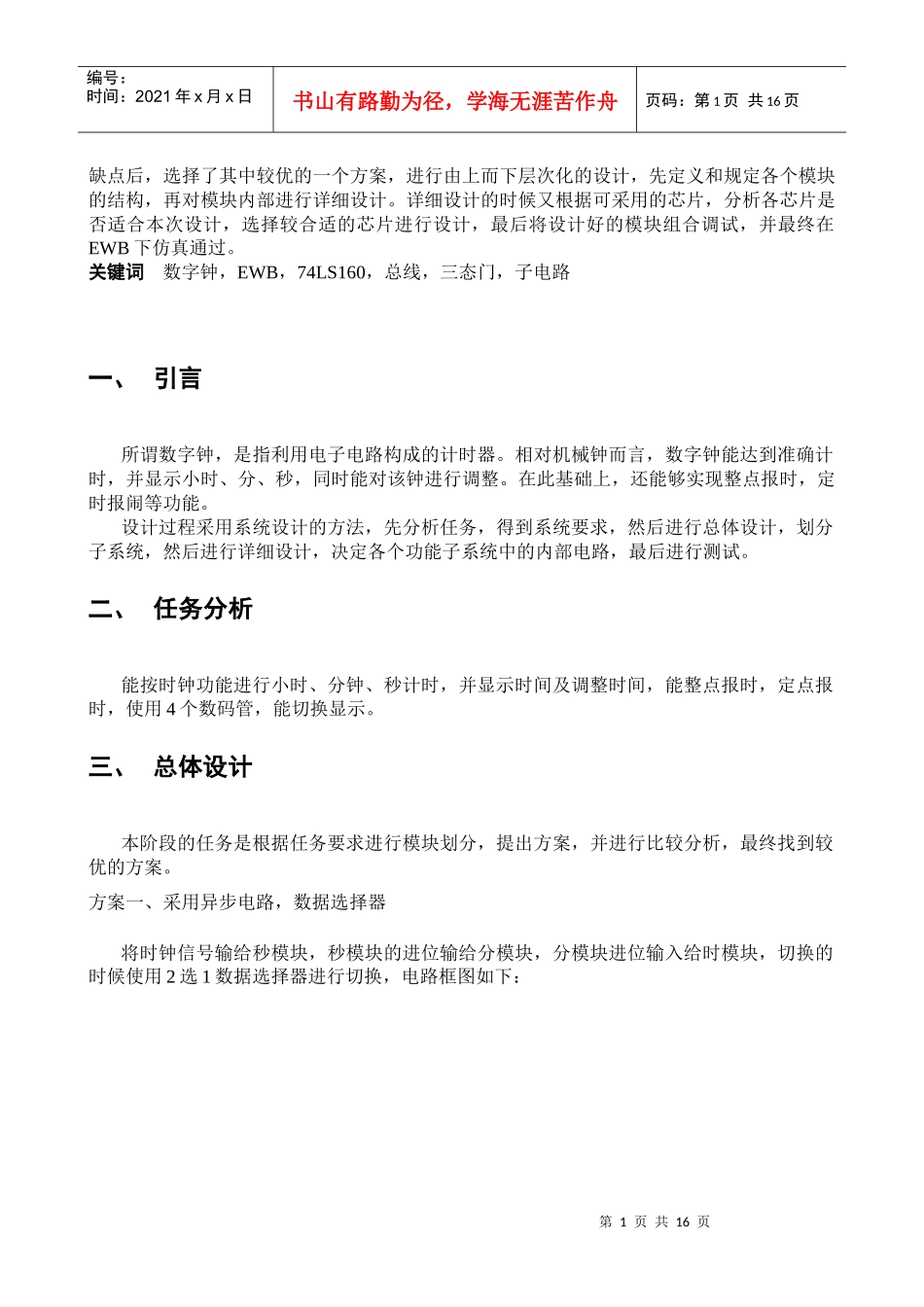

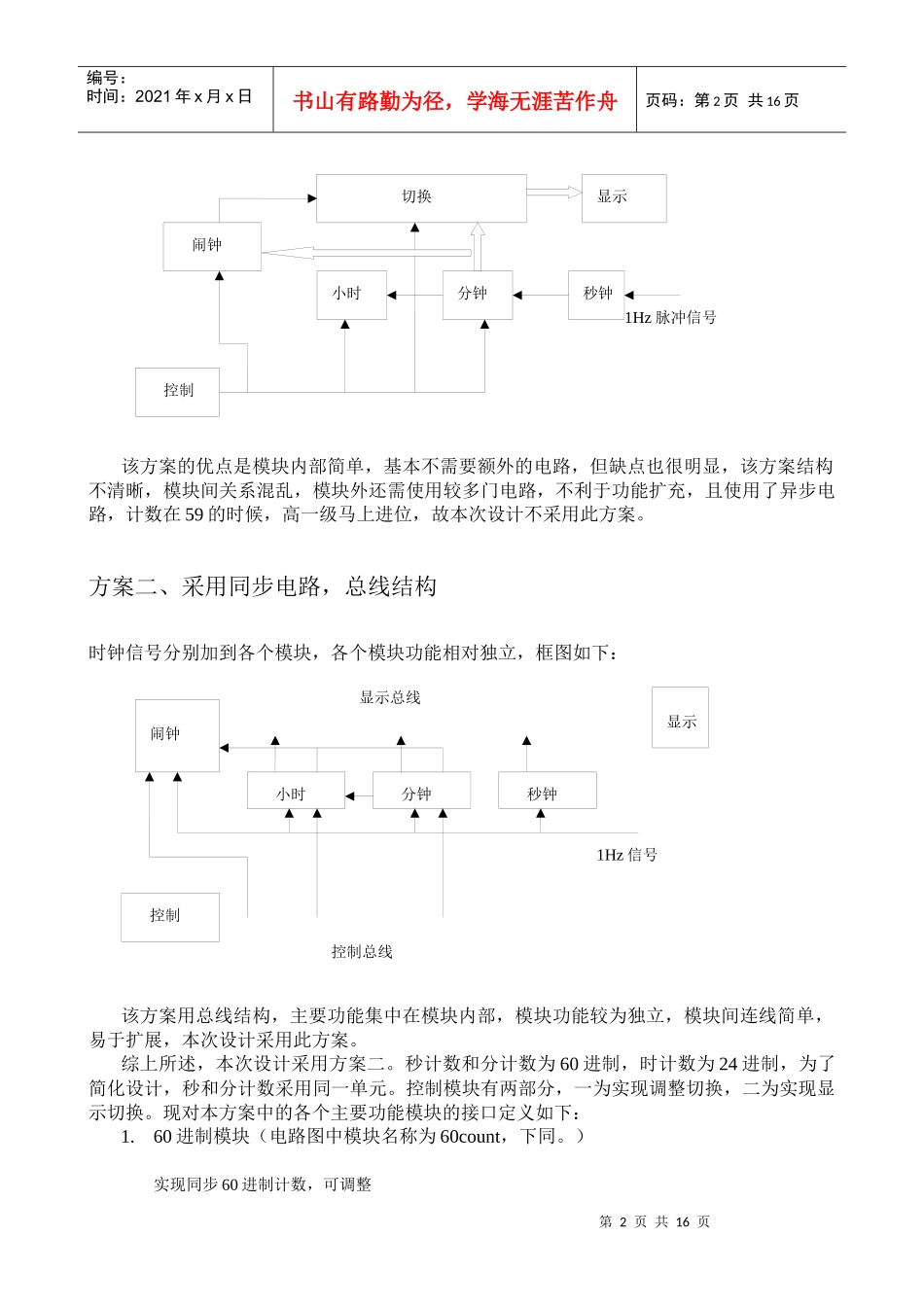

电子技术课程设计报告题目:数字时钟的设计专业:应用电子技术班级:电子091班学号:200905070301姓名:樊丽红指导教师:章华幸设计日期:2011.12.19~2011.12.20摘要本文针对简易数字钟的设计要求,提出了两种整体设计方案,在比较两个方案的优第1页共16页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第1页共16页缺点后,选择了其中较优的一个方案,进行由上而下层次化的设计,先定义和规定各个模块的结构,再对模块内部进行详细设计。详细设计的时候又根据可采用的芯片,分析各芯片是否适合本次设计,选择较合适的芯片进行设计,最后将设计好的模块组合调试,并最终在EWB下仿真通过。关键词数字钟,EWB,74LS160,总线,三态门,子电路一、引言所谓数字钟,是指利用电子电路构成的计时器。相对机械钟而言,数字钟能达到准确计时,并显示小时、分、秒,同时能对该钟进行调整。在此基础上,还能够实现整点报时,定时报闹等功能。设计过程采用系统设计的方法,先分析任务,得到系统要求,然后进行总体设计,划分子系统,然后进行详细设计,决定各个功能子系统中的内部电路,最后进行测试。二、任务分析能按时钟功能进行小时、分钟、秒计时,并显示时间及调整时间,能整点报时,定点报时,使用4个数码管,能切换显示。三、总体设计本阶段的任务是根据任务要求进行模块划分,提出方案,并进行比较分析,最终找到较优的方案。方案一、采用异步电路,数据选择器将时钟信号输给秒模块,秒模块的进位输给分模块,分模块进位输入给时模块,切换的时候使用2选1数据选择器进行切换,电路框图如下:第2页共16页第1页共16页显示切换秒钟分钟小时控制1Hz脉冲信号闹钟闹钟小时分钟秒钟显示控制显示总线控制总线1Hz信号编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第2页共16页该方案的优点是模块内部简单,基本不需要额外的电路,但缺点也很明显,该方案结构不清晰,模块间关系混乱,模块外还需使用较多门电路,不利于功能扩充,且使用了异步电路,计数在59的时候,高一级马上进位,故本次设计不采用此方案。方案二、采用同步电路,总线结构时钟信号分别加到各个模块,各个模块功能相对独立,框图如下:该方案用总线结构,主要功能集中在模块内部,模块功能较为独立,模块间连线简单,易于扩展,本次设计采用此方案。综上所述,本次设计采用方案二。秒计数和分计数为60进制,时计数为24进制,为了简化设计,秒和分计数采用同一单元。控制模块有两部分,一为实现调整切换,二为实现显示切换。现对本方案中的各个主要功能模块的接口定义如下:1.60进制模块(电路图中模块名称为60count,下同。)实现同步60进制计数,可调整第3页共16页第2页共16页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第3页共16页电源5v时钟信号输入接1Hz的信号源进位输入接秒的进位信号,实现秒功能时,接低电平。进位输出秒模块接分模块,分模块接时模块显示输出接到显示总线,能闪烁闹钟比较信号输出接到闹钟,秒模块悬空整点报时信号输出接到响铃,实现3短1长响铃调整使能端入0有效,有效时,显示信号输出,同时屏蔽进位输入和进位输出,允许调整信号输入。显示使能端入0有效调整信号输入2.24进制模块(24count)实现同步24进制计数,可调整电源,时钟信号同上进位输入接分的进位信号进位输出秒模块接分模块,分模块接时模块显示输出同上闹钟比较信号输出接到闹钟调整使能端,显示使能端,调整信号输入同上3.闹钟模块(60clock,24clock)实现可与时钟比较,并输出闹铃信号,可调整电源,时钟信号同上闹钟比较信号输入秒模块接分模块,分模块接时模块显示输出同上闹铃输出接到蜂鸣器调整使能端,显示使能端,调整信号输入同上4.控制模块(fun,func)管理总线资源,对各个模块输出控制信号电源5vVCC调整切换信号接各个需要调整的模块调整信号接到各个需要调整的模块显示切换信号接到各个需要共享显示总线的模块第4页共16页第3页共16页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第4页共16页控制信号输出接到各个模块,有且只能有1个为0至此,本...