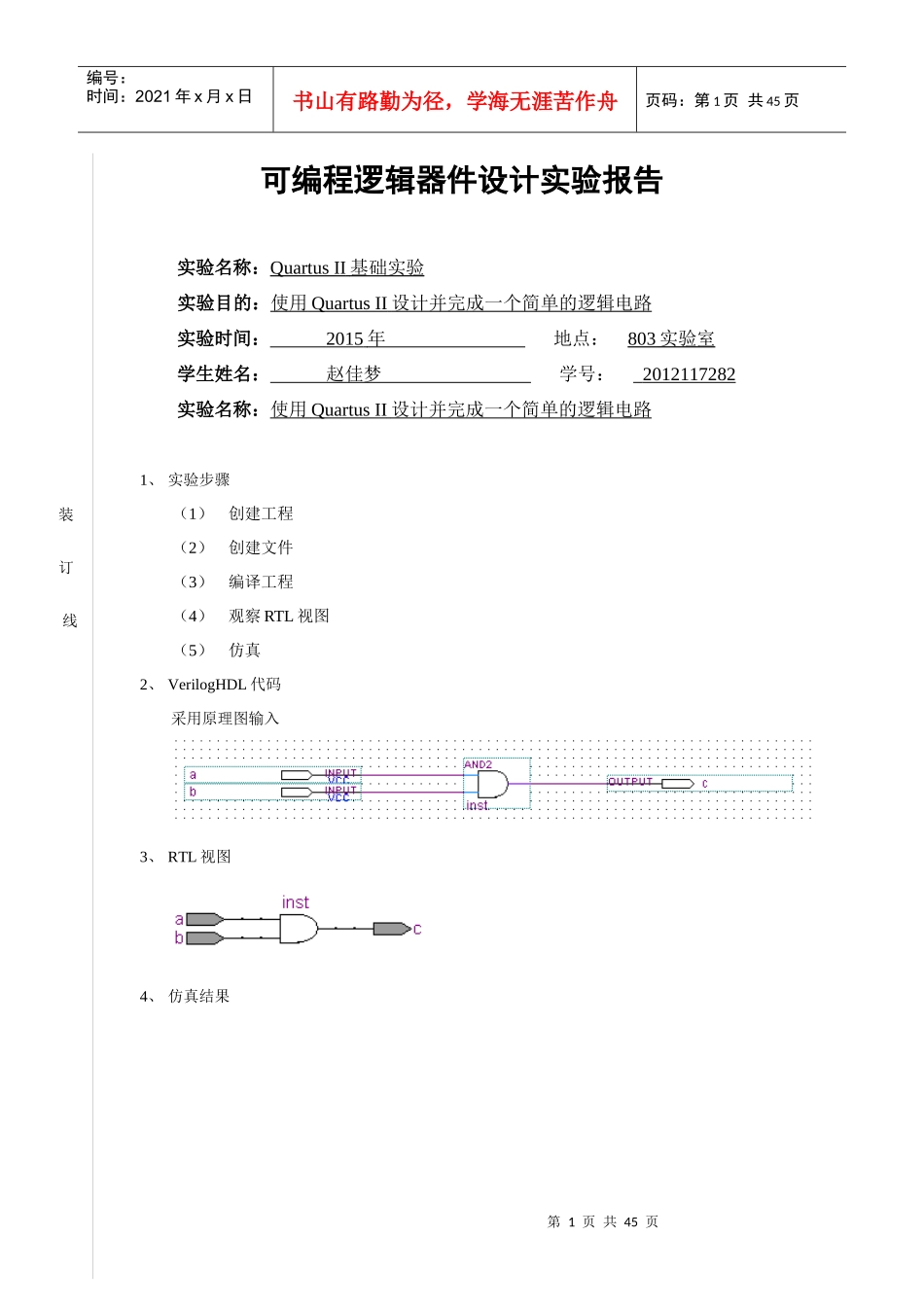

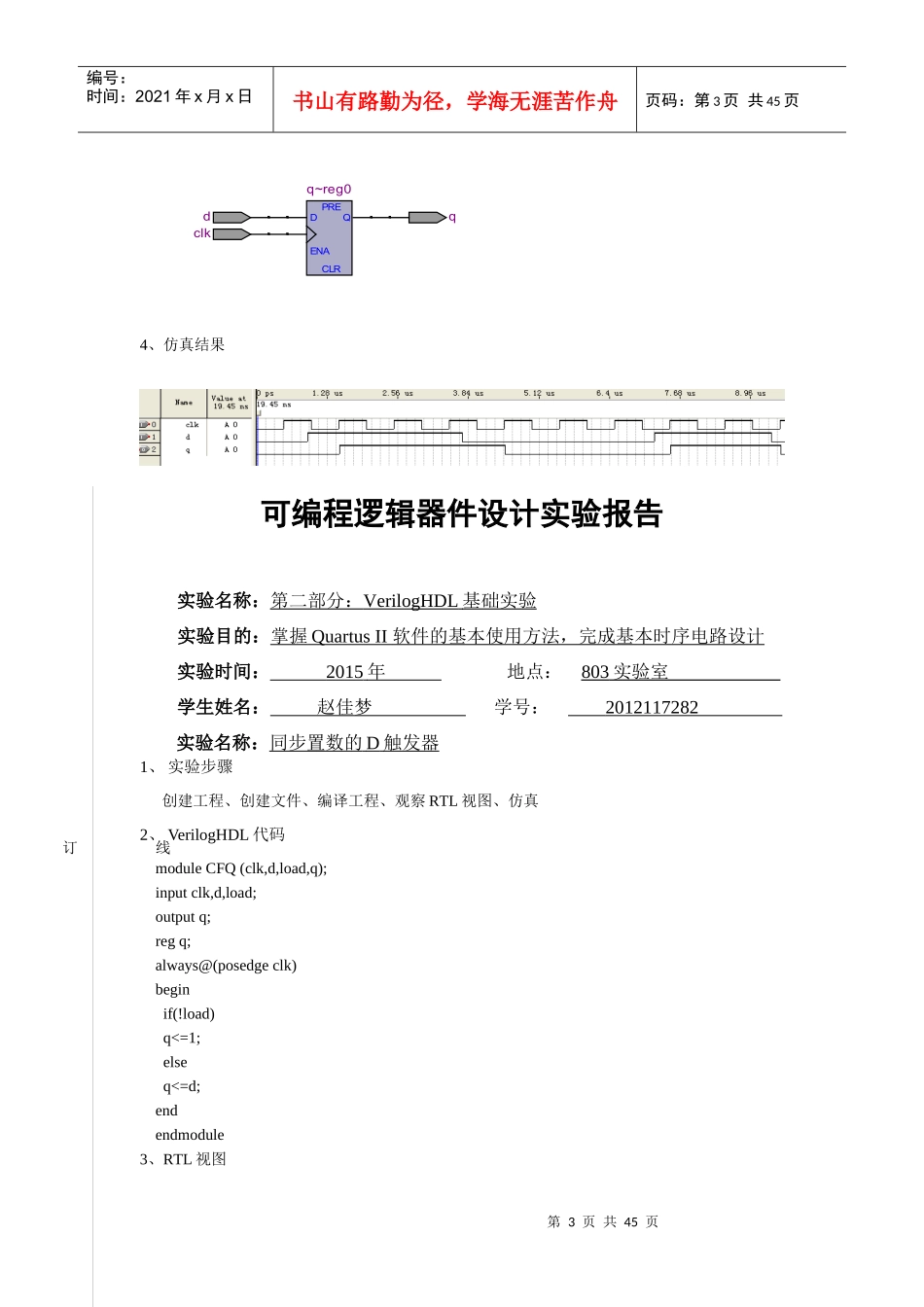

第1页共45页装订线编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第1页共45页可编程逻辑器件设计实验报告实验名称:QuartusII基础实验实验目的:使用QuartusII设计并完成一个简单的逻辑电路实验时间:2015年地点:803实验室学生姓名:赵佳梦学号:2012117282实验名称:使用QuartusII设计并完成一个简单的逻辑电路1、实验步骤(1)创建工程(2)创建文件(3)编译工程(4)观察RTL视图(5)仿真2、VerilogHDL代码采用原理图输入3、RTL视图4、仿真结果第2页共45页第1页共45页装订线编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第2页共45页可编程逻辑器件设计实验报告实验名称:第二部分:VerilogHDL基础实验实验目的:掌握QuartusII软件的基本使用方法,完成基本时序电路设计实验时间:2015年地点:803实验室学生姓名:赵佳梦学号:2012117282实验名称:简单D触发器1、实验步骤(1)创建工程(2)创建文件(3)编译工程(4)观察RTL视图(5)仿真2、VerilogHDL代码module_DFF(clk,d,q);inputclk,d;outputq;regq;always@(posedgeclk)beginq<=d;endendmodule3、RTL视图第3页共45页第2页共45页装订线编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第3页共45页DENAQPRECLRclkqdq~reg04、仿真结果可编程逻辑器件设计实验报告实验名称:第二部分:VerilogHDL基础实验实验目的:掌握QuartusII软件的基本使用方法,完成基本时序电路设计实验时间:2015年地点:803实验室学生姓名:赵佳梦学号:2012117282实验名称:同步置数的D触发器1、实验步骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、VerilogHDL代码moduleCFQ(clk,d,load,q);inputclk,d,load;outputq;regq;always@(posedgeclk)beginif(!load)q<=1;elseq<=d;endendmodule3、RTL视图第4页共45页第3页共45页装订线编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第4页共45页011DENAQPRECLRq~0clkdloadqq~reg04、仿真结果可编程逻辑器件设计实验报告实验名称:第二部分:VerilogHDL基础实验实验目的:掌握QuartusII软件的基本使用方法,完成基本时序电路设计实验时间:2015年地点:803实验室学生姓名:赵佳梦学号:2012117282实验名称:同步置数异步清零的D触发器1、实验步骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、VerilogHDL代码module_DFf(clk,d,load,rest,q);inputclk,d,load,rest;outputq;regq;always@(posedgeclkornegedgerest)beginif(!rest)q<=0;elseif(!load)q<=1;第5页共45页第4页共45页装订线编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第5页共45页elseq<=d;endendmodule3、RTL视图01DENAQPRECLR1q~reg0clkdloadrestqq~04、仿真结果可编程逻辑器件设计实验报告实验名称:第二部分:VerilogHDL基础实验实验目的:掌握QuartusII软件的基本使用方法,完成基本时序电路设计实验时间:2015年地点:803实验室学生姓名:赵佳梦学号:2012117282实验名称:带Q_n输出的D触发器1、实验步骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、VerilogHDL代码moduled_q(in,clk,q,set,a,reset,q_n);inputclk,in,set,a,reset;outputregq,q_n;always@(posedgeclk,negedgereset)beginq_n=~q;if(!reset)q<=0;elseif(!set)第6页共45页第5页共45页装订线编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第6页共45页q<=a;elseq<=in;end3、RTL视图4、仿真结果可编程逻辑器件设计实验报告实验名称:第二部分:VerilogHDL基础实验实验目的:掌握QuartusII软件的基本使用方法,完成基本时序电路设计实验时间:2015年地点:803实验室学生姓名:赵佳梦学号:2012117282实验名称:4选1数据选择器1、实验步骤创建工程、创建文件、编译工程、观察RTL视图、仿真2、VerilogHDL代码modulemux4_1(in0,in1,in2,in3,s0,s1,out);inputs0,s1;inputin0,in1,in2,in3;outputout;regout;always@(in0,in1,in2,in3,s0,s1)begin第7页共45页第6页共45页装订线编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第7页共45页case({s0,s1})...