译文基于FPGA的串行控制器设计ThomasOelsnerQuickLogicEurope应用注释:QAN20简介目前设计开发和验证FPGA系统时,硬件描述语言HDL的使用变得越来越主流

采用行为级描述不仅提高了产品的设计效率,而且在设计验证中显示出其独特的优势

目前最流行的HDL语言是Verilog和VHDL语言

本文介绍了采用verilog语言对数字异步串行收发器进行设计和验证

UART通用异步串行收发器(UART)由二个独立的HDL模块组成

一个模块实现发射功能,而另一个模块则实现接收功能

发射和接收功能模块在顶层设计时组合到一起,这种接收和发射的组合是通信所必需的

数据写入发射器,从接收器读出,所有的数据是以二进制8字节的形式通过一个双向CPU接口

由地址映射的发射机和接收机通道可以很容易地建立接口

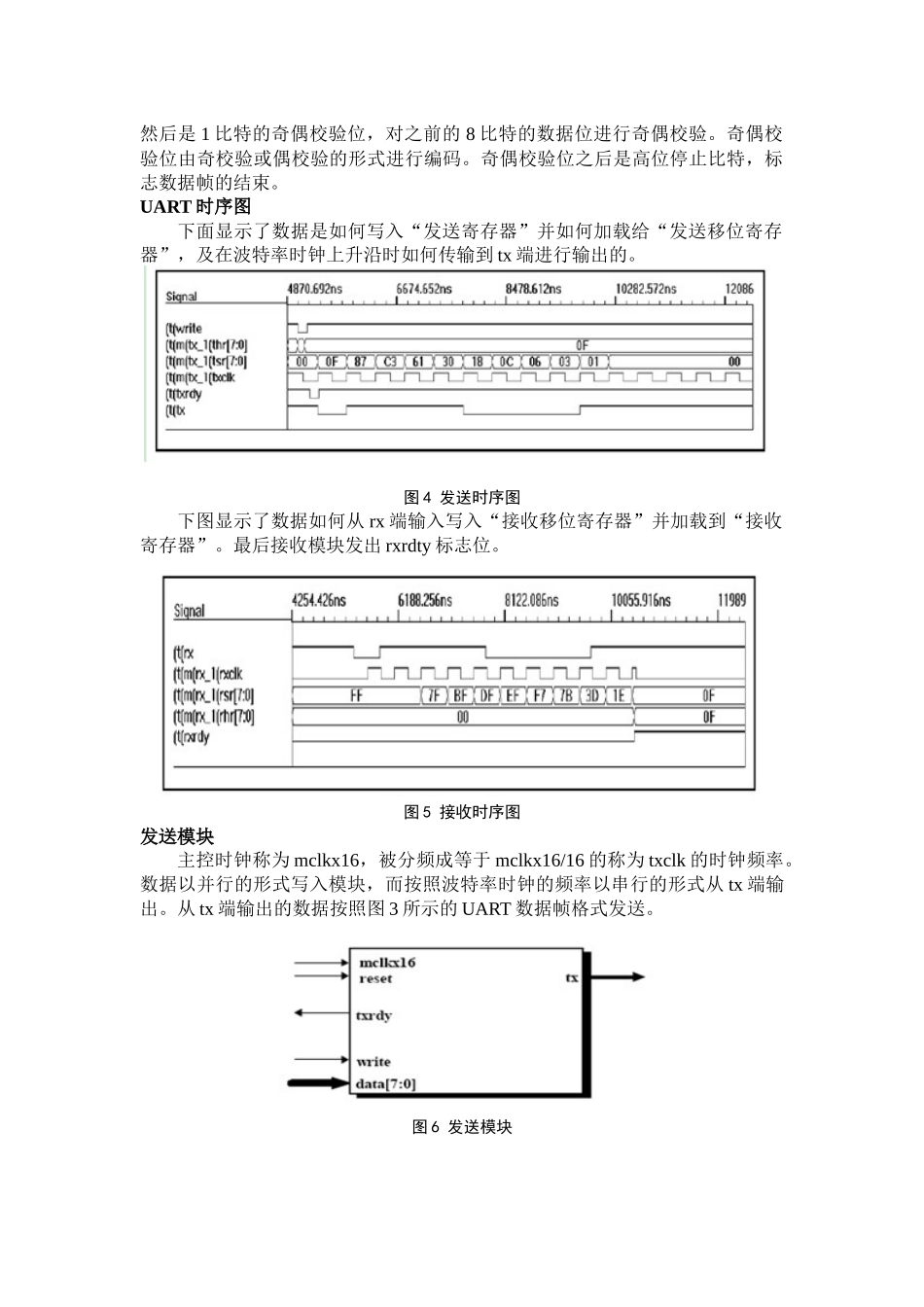

两个模块共用一个主控时钟,该时钟为mclkx16,在每个模块里,主控时钟mclkx16被分频成独立的波特率时钟

图1通用异步串行收发器通用异步串行收发器的特点是否具有全双工操作标准UART数据帧格式偶校验或奇校验模式奇偶错误校验帧错误校验溢出错误校验数据接收准备中断数据发送准备中断是是是是是是是是表UART功能概述UART的功能概况UART的基本功能概况见下图

左边为“发送寄存器”、“发送移位寄存器”以及“发送控制逻辑模块”,这些模块包含在发送模块”txmix”中

右边为“接收移位寄存器”、“接收寄存器”和“接收控制逻辑模块”,这些模块包含在发送模块”rxmix”中

这两个模块有单独的输入和输出的控制线路,只有双向的数据总线、主时钟和复位线是共享的

图2UART框图顶层UART系统的I/O功能描述符号类型描述mclkx16输入用于主控时钟波特率的生产

reset输入主复位输入信号

parityerr输出表明被检测的数据帧有无奇偶校验错误

校验编码可以基于偶数或奇数模式