本科课程设计报告(2016至2017学年第一学期)设计题目:基于TMS320F28335DSP微处理器的最小系统设计课程名称:数字信号处理专业名称:电子信息工程行政班级:1313学号:1313姓名:洪指导教师:赵报告时间:2016年10月23日目录一、引言TMS320F28335型数字信号处理器TI公司的一款TMS320C28X系列浮点DSP控制器

与以往的定点DSP相比,该器件精度高,成本低,功耗小,性能高,外设集成度高,数据以及程序存储量大,A/D转换更精确快速等

TMS320F28335具有150MHz的高速处理能力,具备32位浮点处理单元,6个DMA通道支持ADC、McBSP和EMIF,有多达18路的PWM输出,其中有6路为TI特有的更高精度的PWM输出(HRPWM),12位16通道ADC

得益于其浮点运算单元,用户可快速编写控制算法而无需在处理小数操作上耗费过多的时间和精力,与前代DSC相比,平均性能提高50%,并与定点C28x控制器软件兼容,从而简化软件开发,缩短开发周期,降低开发成本

F2833X在保持150MHz时钟速率不变的情况下,新型F2833X浮点控制器与TI前代领先数字信号控制器相比,性能平均提高50%

与作用相当的32位定点技术相比,快速傅立叶转换(FFT)等复杂计算算法采用新技术后性能提升了一倍之多

二、设计目的TMS320F28335及其最小应用系统是最基本的硬件和软件环境

设计目的是能使用Protel设计电路原理图;了解F28335硬件的相关知识及电路设计;能使用CCS建立并调试DSP工程

通过F28335最小电路的设计,可以将理论与实践统一联系,更深入地理解F28335的开发方法

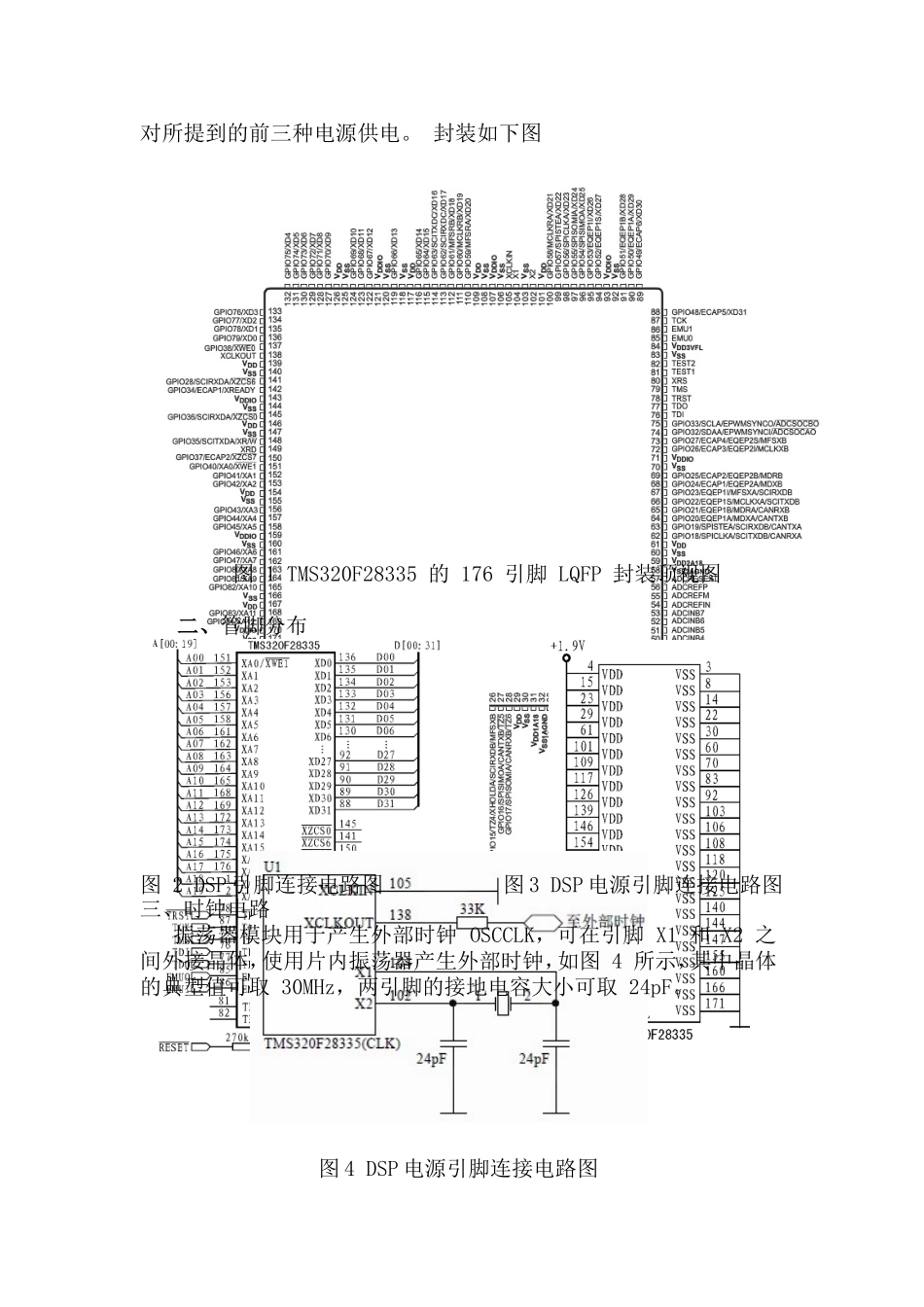

三、设计要求1、利用Protel软件绘制并添加TMS320F28335的原理图库;2、利用Protel软件绘制TMS320F28335最小系统的电路原理图,包括时