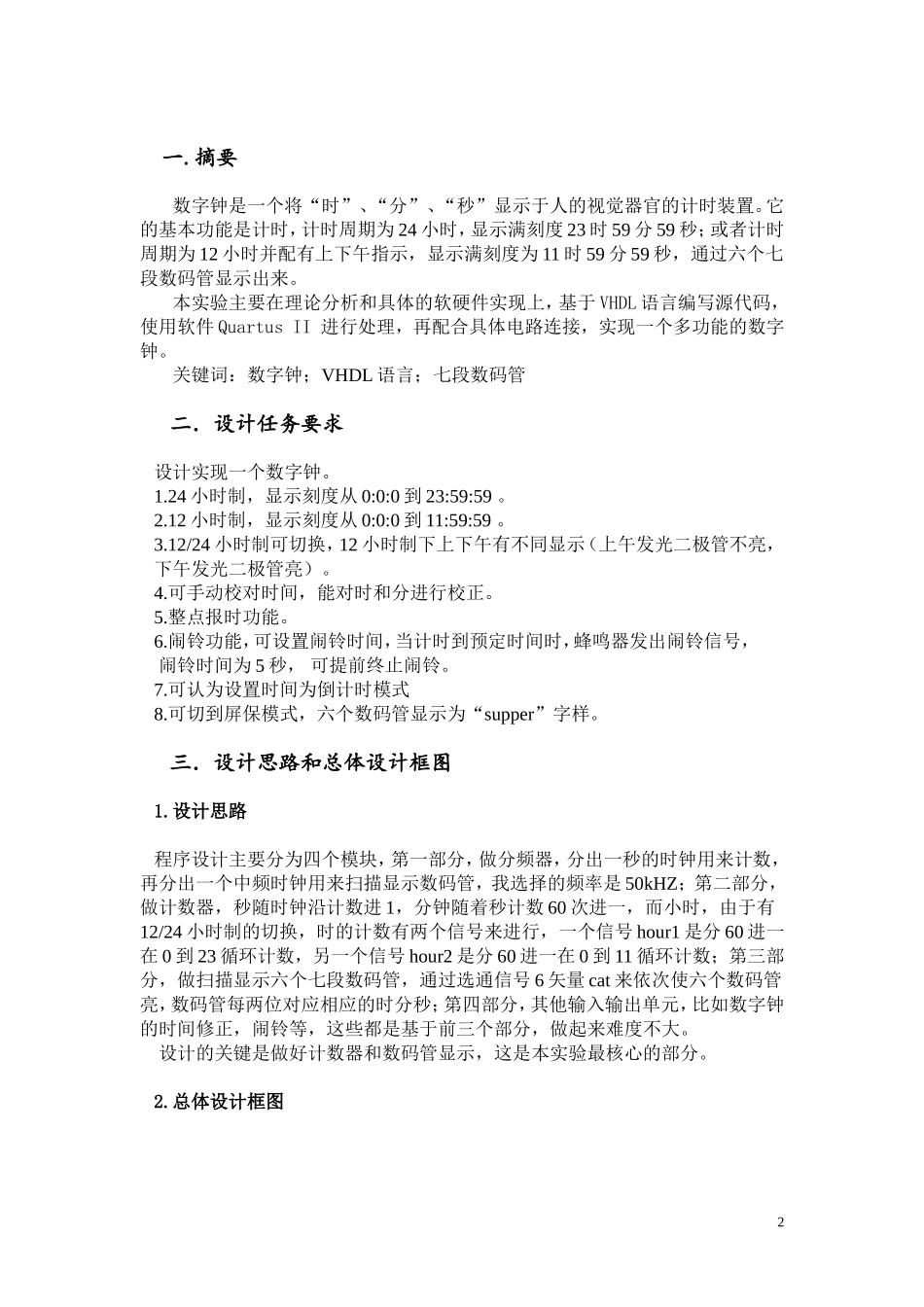

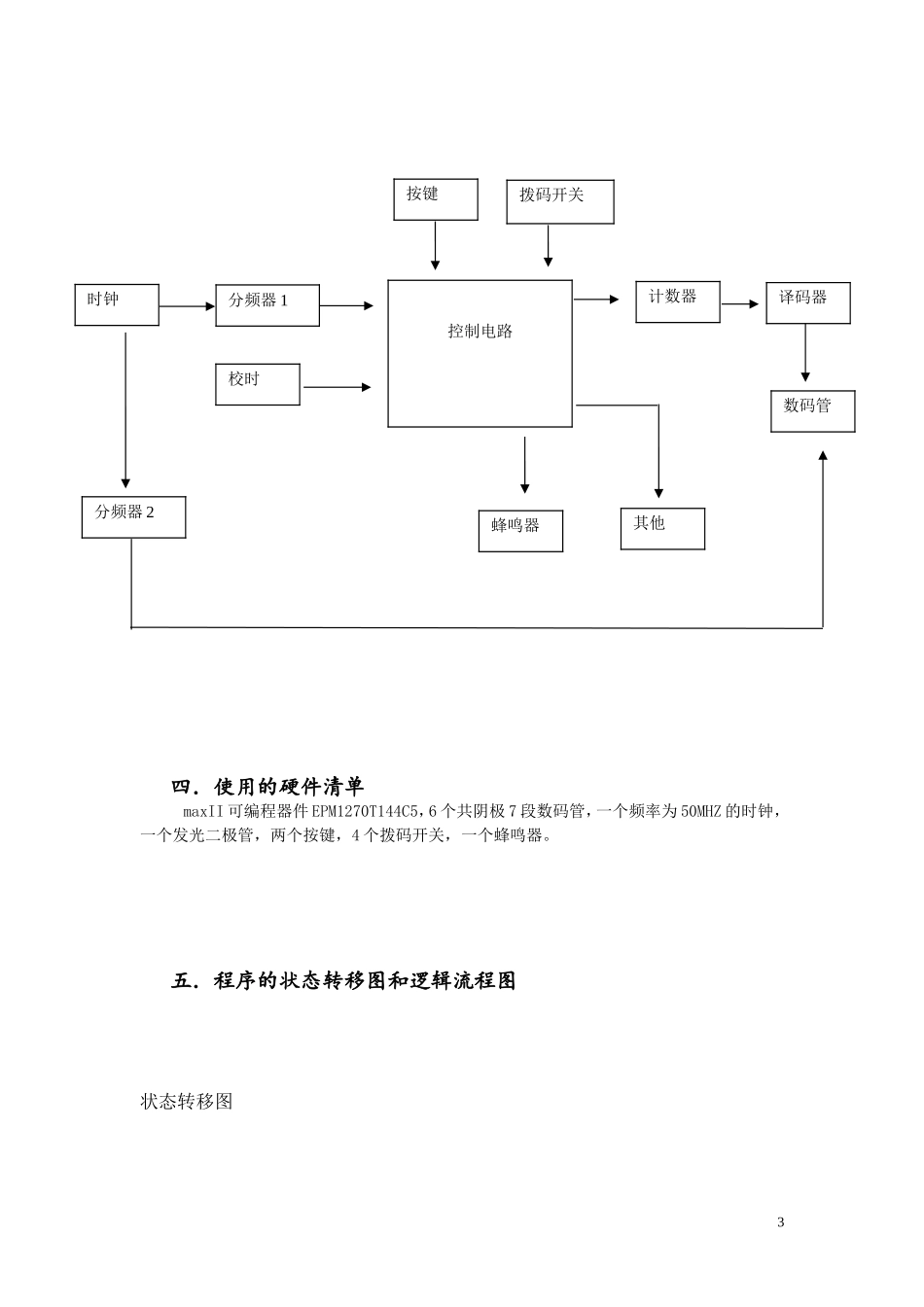

信息与通信工程学院数字电路与逻辑设计实验题目:基于VHDL语言的数字钟设计班级:姓名:学号:日期:指导教师:1一.摘要数字钟是一个将“时”、“分”、“秒”显示于人的视觉器官的计时装置。它的基本功能是计时,计时周期为24小时,显示满刻度23时59分59秒;或者计时周期为12小时并配有上下午指示,显示满刻度为11时59分59秒,通过六个七段数码管显示出来。本实验主要在理论分析和具体的软硬件实现上,基于VHDL语言编写源代码,使用软件QuartusII进行处理,再配合具体电路连接,实现一个多功能的数字钟。关键词:数字钟;VHDL语言;七段数码管二.设计任务要求设计实现一个数字钟。1.24小时制,显示刻度从0:0:0到23:59:59。2.12小时制,显示刻度从0:0:0到11:59:59。3.12/24小时制可切换,12小时制下上下午有不同显示(上午发光二极管不亮,下午发光二极管亮)。4.可手动校对时间,能对时和分进行校正。5.整点报时功能。6.闹铃功能,可设置闹铃时间,当计时到预定时间时,蜂鸣器发出闹铃信号,闹铃时间为5秒,可提前终止闹铃。7.可认为设置时间为倒计时模式8.可切到屏保模式,六个数码管显示为“supper”字样。三.设计思路和总体设计框图1.设计思路程序设计主要分为四个模块,第一部分,做分频器,分出一秒的时钟用来计数,再分出一个中频时钟用来扫描显示数码管,我选择的频率是50kHZ;第二部分,做计数器,秒随时钟沿计数进1,分钟随着秒计数60次进一,而小时,由于有12/24小时制的切换,时的计数有两个信号来进行,一个信号hour1是分60进一在0到23循环计数,另一个信号hour2是分60进一在0到11循环计数;第三部分,做扫描显示六个七段数码管,通过选通信号6矢量cat来依次使六个数码管亮,数码管每两位对应相应的时分秒;第四部分,其他输入输出单元,比如数字钟的时间修正,闹铃等,这些都是基于前三个部分,做起来难度不大。设计的关键是做好计数器和数码管显示,这是本实验最核心的部分。2.总体设计框图2四.使用的硬件清单maxII可编程器件EPM1270T144C5,6个共阴极7段数码管,一个频率为50MHZ的时钟,一个发光二极管,两个按键,4个拨码开关,一个蜂鸣器。五.程序的状态转移图和逻辑流程图状态转移图3控制电路计数器时钟分频器1校时按键译码器数码管蜂鸣器其他拨码开关分频器2fixnamenamefixchclarmch逻辑流程图4启动计数24时计数分频显示校时12时计数屏保闹铃是否是否是是否六.完整的源程序6数码管显示时钟,带调时功能,能设置闹钟,闹钟响可人为停止,整点报时,12/24小时制手动切换,可人为设置时间为倒计时,并修正了一个11:59:59(或23:59:59)跳变到00:00:00的bug(即11:59:59跳变到00:00:00时会先跳到11:00:00再跳到00:00:00的错误),不足是防抖动设计缺少经验。--madebysupper5校时整点响铃1闹钟响铃2显示调时定时libraryieee;useieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entitymemclockisport(clk:instd_logic;mfix,hfix:instd_logic;change:instd_logic;last:instd_logic;ld0:outstd_logic;name:instd_logic;alarm:instd_logic;cat:outstd_logic_vector(5downto0);spk:outstd_logic;light:outstd_logic_vector(6downto0));endmemclock;architecturebehaveofmemclockissignaltemp:integerrange0to15;signalj:integerrange0to5;signalclk1,clk2:std_logic;signalminute:integerrange0to59;signalsecond:integerrange0to59;signalhour,hour1:integerrange0to23;signalhour2:integerrange0to11;signalh0,h1,m0,m1,s0,s1:integerrange0to15;signaltmp1:integerrange0to499999999;signaltmp2:integerrange0to999;6signalho:integerrange0to23;signalmin:integerrange0to59;beginp0:process(clk)beginif(clk'eventandclk='1')theniftmp1=49999999thentmp1<=0;elsetmp1<=tmp1+1;endif;if(tmp2=999)thentmp2<=0;elsetmp2<=tmp2+1;endif;endif;endprocess;p5:process(tmp1)beginiftmp1=49999999thenclk1<='1';elseclk1<='0';endif;iftmp2=999then7clk2<='1';elseclk2<='0';endif;endprocess;p1:process(clk1)beginif(clk1'eventandclk1='1')thenif(last='...