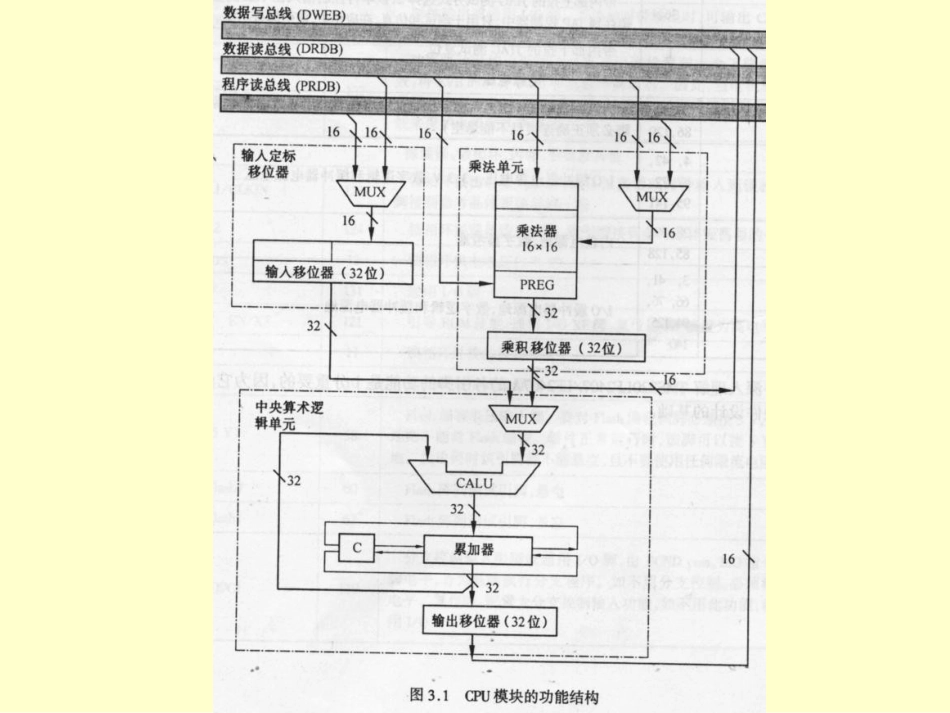

第3章TMS320LF240x的CPU功能模块和时钟模块本章介绍TMS320LF240x的CPU模块和时钟模块。3.1CPU功能模块TMS320LF240x的CPU模块包括:输入定标移位器、中央算术逻辑单元(CALU)和乘法器等。CPU模块的功能结构如图3.1所示。3.1.1输入定标移位器LF240xDSP的CPU输入定标移位器将来自程序/数据存储器的16位数据调整为32位数据送到中央算术逻辑单元(CALU)。因此,输入定标移位器的16位输入与数据总线相连,32位输出与CALU单元相连。该输入定标移位器在算术定标以及逻辑操作设置时非常有用。输入定标移位器对输入数据进行0-15位左移。左移时,输出的最低有效位(LSB)为0,最高有效位(MSB)根据状态寄存器ST1(将在3.1.6小节介绍)的SXM位(符号扩展方式)的值来决定是否需要进行符号扩展。当SXM=1时,则高位进行符号扩展;当SXM=0时,则高位填0。移位的次数由包含在指令中的常量或临时寄存器(TREG)中的值来指定。3.1.2乘法器LF240x采用一个1616☓位的硬件乘法器,可以在单个机器周期内产生一个32位的有符号或无符号乘积。除了执行无符号乘法指令(MPYU)外,所有的乘法指令均执行有符号的乘法操作,即相乘的两个数都作为二进制的补码数,而运算结果为一个32位的二进制的补码数。乘法器接收的两个乘数,一个来自16位的临时寄存器(TREG),另一个通过数据读总线(DRDB)取自数据存储器,或通过程序读总线(PRDB)取自程序存储器。两个输入值相乘后,32位的乘积结果保存在32位的乘积寄存器(PREG)中。PREG的输出连接到乘积定标移位器,通过乘积定标移位器,乘积结果可以从PREG传到CALU或数据存储器乘积定标移位器对乘积的结果采用4种乘积移位方式,如表3.1所示。移位方式由状态寄存器ST1的乘积移位方式位(PM)指定。这些移位方式对于执行乘法/累加操作、进行小数运算或者进行小数乘积的调整都很有用。表3.1乘积定标移位器的乘积移位方式PM移位作用和意义00无移位乘积送CALU或数据写总线,不移位01左移1位移去二进制补码乘法产生的额外符号位,产生Q31格式的乘积10左移4位当与一个13位的常数相乘时,移去在1613☓位(常数)二进制补码产生的额外的4位符号位,产生Q31格式的乘积11右移6位对乘积结果定标,以使得运行128次的乘积累加而累加器不会溢出3.1.3中央算术逻辑单元及累加器中央算术逻辑单元(CALU)实现大部分算术和逻辑运算功能,大多数功能只需一个时钟周期,这些运算功能包括:16位加、16位减、布尔运算、位测试以及移位和循环功能。由于CALU可以执行布尔运算,因此使得控制器具有位操作功能。CALU的移位和循环在累加器中完成。CALU是一个独立的算术单元,它和后面介绍的辅助寄存器算术单元(ARAU)在程序执行时,是完全不同的两个模块。LF240xDSP中央算术逻辑单元(CALU)实现大部分算术和逻辑运算功能,而且大多数的功能只需1个机器周期。一旦操作在CALU中被执行,运算结果会被传送到累加器中,在累加器中再实现附加操作,如移位等操作。CALU是一个通用目标算术逻辑单元,它可以对来自数据存储器或者来自立即操作指令的16位数进行算术运算或布尔运算,使高速控制器所要求的位操作很容易。CALU有两个输入,一个由累加器提供,另一个由乘积寄存器(PREG)或数据定标移位器的输出提供。当CALU执行完一次操作后将结果送至32位累加器,由累加器对其结果进行移位。累加器的输出送到32位输出数据定标移位器,经过输出数据定标移位器,累加器的高、低16位字可分别被移位或存入数据寄存器。CALU的溢出饱和方式可以由状态寄存器ST0(见3.1.6小节的介绍)的溢出模式(OVM)位来使能或禁止。根据CALU和累加器的状态,CALU可执行各种分支指令。这些指令可以根据这些状态位有意义的结合有条件地执行。为了溢出管理,这些条件包括OV(根据溢出跳转)和EQ(根据累加器是否为0跳转)等。另外,BACC(跳到累加器的地址)指令可以跳转到由累加器所指定的地址;不影响累加器的位测试指令(BIT和BITT);允许对数据存储器中的一个字的指定位进行测试。对绝大多数的指令,状态寄存器ST1的第10位符号扩展位(SXM)决定了在CALU计算时是否使用符号扩展。SXM=0,符号扩展无效,SXM=1,符号扩展有效。3.1...