第2章TMS320C54x数字信号处理器硬件结构•2

1TMS320C54x的特点和硬件组成框图•2

2TMS320C54x的总线结构•2

3TMS320C54x的存储器分配•2

4中央处理单元(CPU)•2

5TMS320C54x片内外设简介•2

6硬件复位操作•2

7TMS320VC5402引脚及说明2

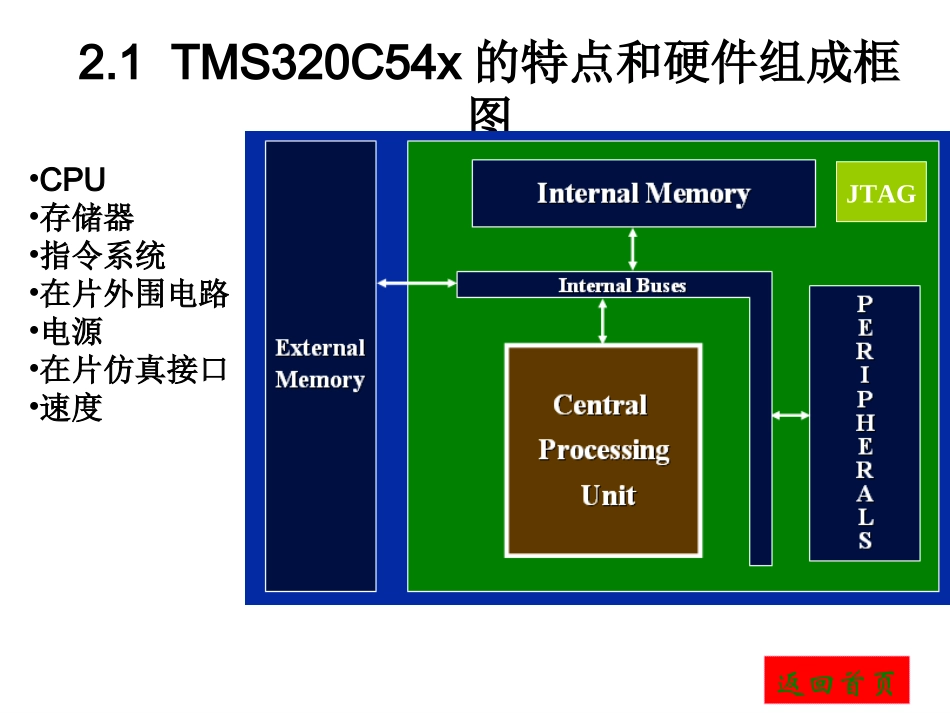

1TMS320C54x的特点和硬件组成框图返回首页JTAG•CPU•存储器•指令系统•在片外围电路•电源•在片仿真接口•速度CPU(如图2-1所示)•先进的多总线结构

•40位算术逻辑运算单元(ALU)

•17位×17位并行乘法器与40位专用加法器相连

•比较、选择、存储单元(CSSU)

•指数编码器可以在单个周期内计算40位累加器中数值的指数

•双地址生成器包括8个辅助寄存器和两个辅助寄存器算术运算单元(ARAU)

图2-1TMS320C54xDSP的内部硬件组成框图1多总线双地址生成器片外总线片内外设总线图2-1TMS320C54xDSP的内部硬件组成框图2返回本节算术逻辑运算单元并行乘法器专用加法器比较、选择、存储单元指数编码器桶形移位器累加器存储器•64K字程序存储器、64K字数据存储器以及64K字I/O空间

•在C548、C549、C5402、C5410和C5420中程序存储器可以扩展

程序存储器数据存储器IO空间扩展程序存储器指令系统•单指令重复和块指令重复操作

•块存储器传送指令

•32位长操作数指令

•同时读入两个或3个操作数的指令

•并行存储和并行加载的算术指令

•条件存储指令

•从中断快速返回指令

在片外围电路•软件可编程等待状态发生器

•可编程分区转换逻辑电路

•带有内部振荡器

•外部总线关断控制,以断开外部的数据总线、地址总线和控制信号

•数据总线具有总线保持器特性

•可编程定时器

•并行主机接口(HPl)

电源•可用IDLEl、IDLE2和ID