摘要:本文主要通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束,主要涉及到的约束包括时钟约束、群组约束、逻辑管脚约束以及物理属性约束

XilinxFPGA设计约束的分类Xilinx定义了如下几种约束类型:•“AttributesandConstraints”•“CPLDFitter”•“GroupingConstraints”•“LogicalConstraints”•“PhysicalConstraints”•“MappingDirectives”•“PlacementConstraints”•“RoutingDirectives”•“SynthesisConstraints”•“TimingConstraints”•“ConfigurationConstraints”通过编译UCF(userconstraintsfile)文件可以完成上述的功能

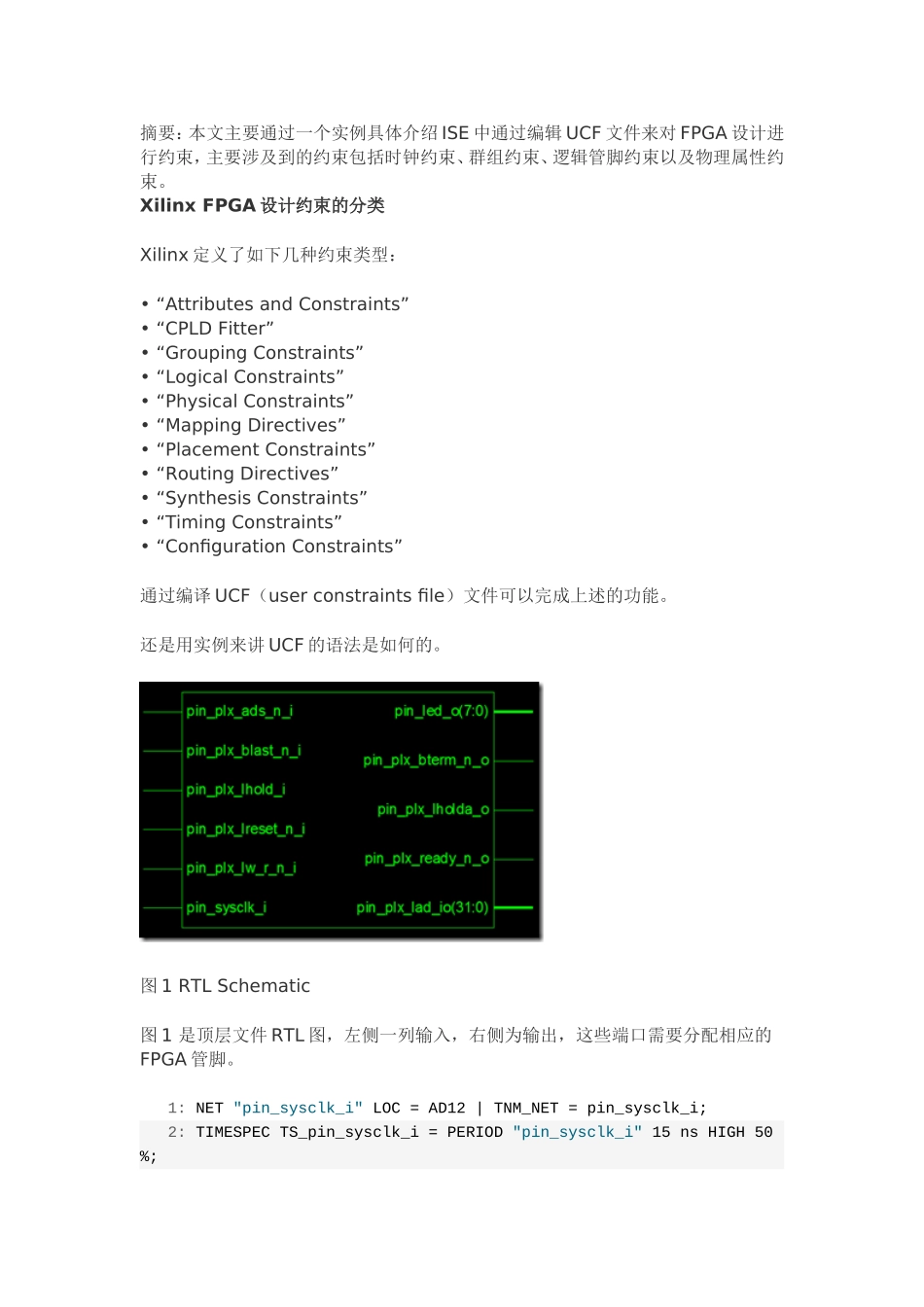

还是用实例来讲UCF的语法是如何的

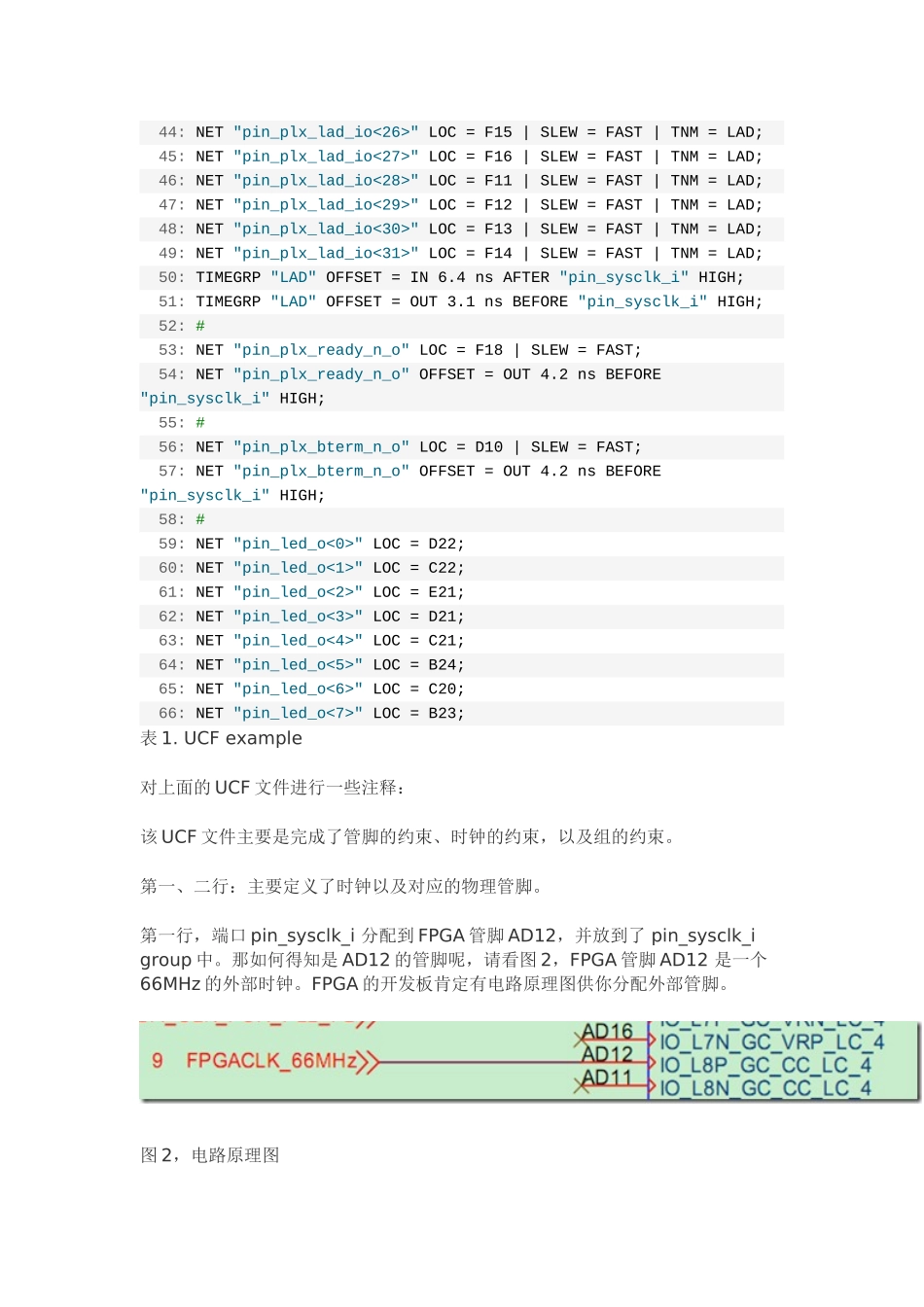

图1RTLSchematic图1是顶层文件RTL图,左侧一列输入,右侧为输出,这些端口需要分配相应的FPGA管脚

1:NET"pin_sysclk_i"LOC=AD12|TNM_NET=pin_sysclk_i;2:TIMESPECTS_pin_sysclk_i=PERIOD"pin_sysclk_i"15nsHIGH50%;3:#4:NET"pin_plx_lreset_n_i"LOC=B18;5:#6:NET"pin_plx_lhold_i"LOC=C17;7:NET"pin_plx_lholda_o"LOC=D17|SLEW=FAST;8:#9:NET"pin_plx_ads_n_i"LOC=E18;10:NET"pin_plx_ads_n_i"OFFSET=IN6

3nsAFTER"pin_sysclk_i"HIGH;11:#12:NET"pin_plx_lw_r