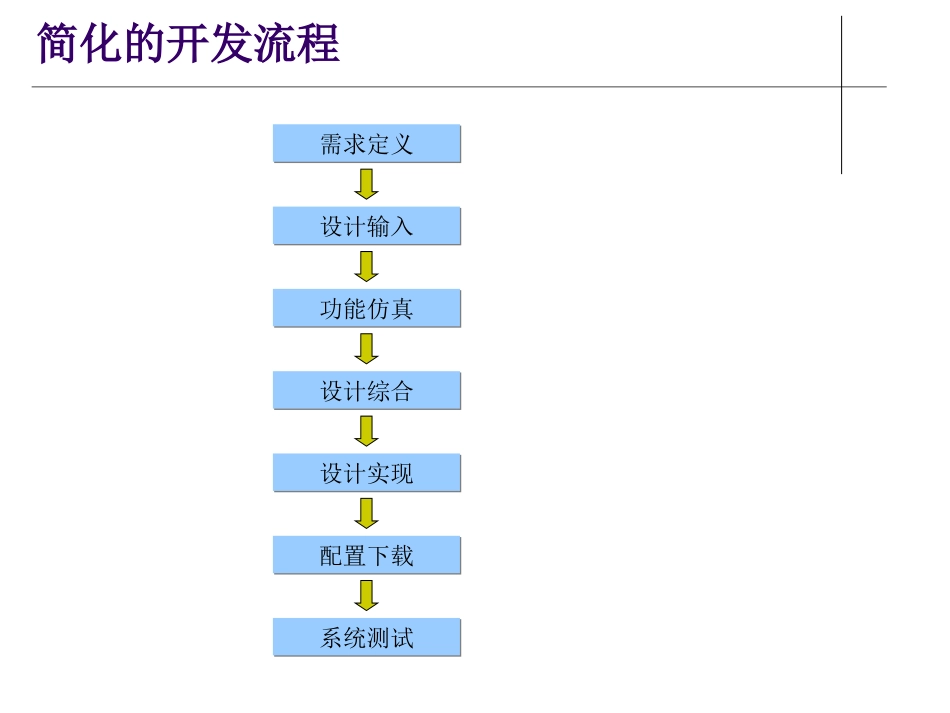

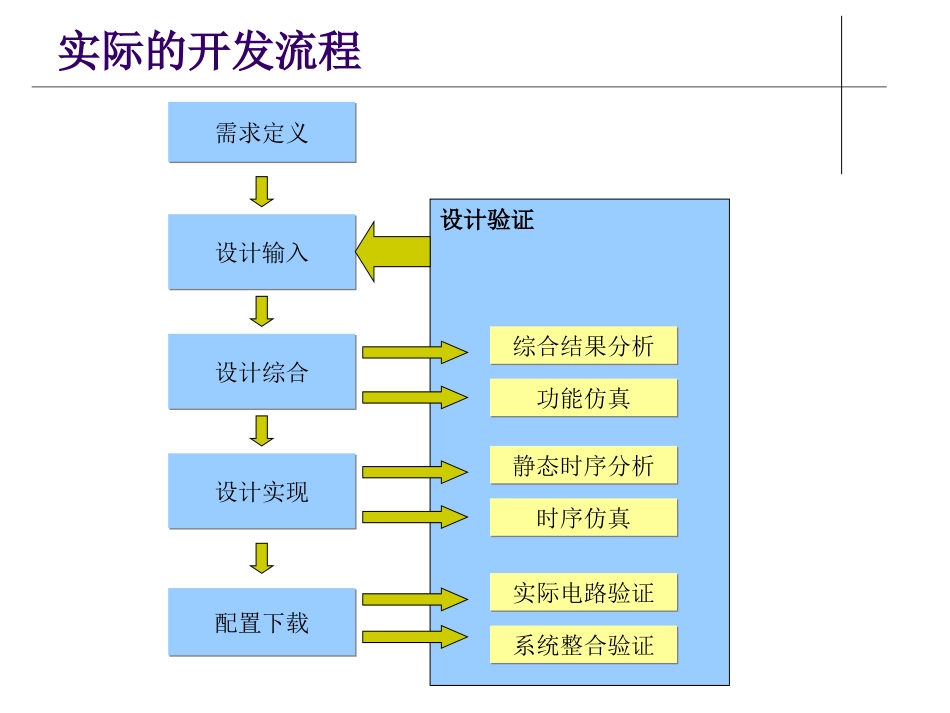

FPGA开发流程及编程思想简化的开发流程需求定义需求定义设计输入设计输入设计综合设计综合设计实现设计实现配置下载配置下载功能仿真功能仿真系统测试系统测试设计验证实际的开发流程需求定义需求定义设计输入设计输入设计综合设计综合设计实现设计实现配置下载配置下载综合结果分析综合结果分析实际电路验证实际电路验证静态时序分析静态时序分析时序仿真时序仿真系统整合验证系统整合验证功能仿真功能仿真需求定义需求决定设计“这个设计是做什么用的

”“要实现什么功能

”“有什么要注意的地方

”需求是容易发生变更的大师说过,没有哪个设计需求更改少于三次的,唯一一次只更改过两次需求的情况,是那个可怜的家伙在送第三次变更需求来的路上,被车给撞了

你不能决定需求是否发生变更,但你可以做到当需求更改时,你所需要做出的调整最小

设计输入原理图输入(对大型设计很少使用)硬件描述语言VerilogHDL,VHDLHDL语言是硬件描述语言,不是硬件设计语言用硬件电路设计思想来编写HDL先有鸡,还是先有蛋

always@(posedgeclk)if(

rst_n)a