静止图像压缩标准JPEGIP核的设计与实现基金颁发部门:福建省科技厅;项目名称:射频开关悬梁振动特性分析及纳米尺度下的触点行为研究;编号:2006J0032基金申请人:于映张志晓1,于映2(1

福州大学物理与信息工程学院,福建福州350002;2

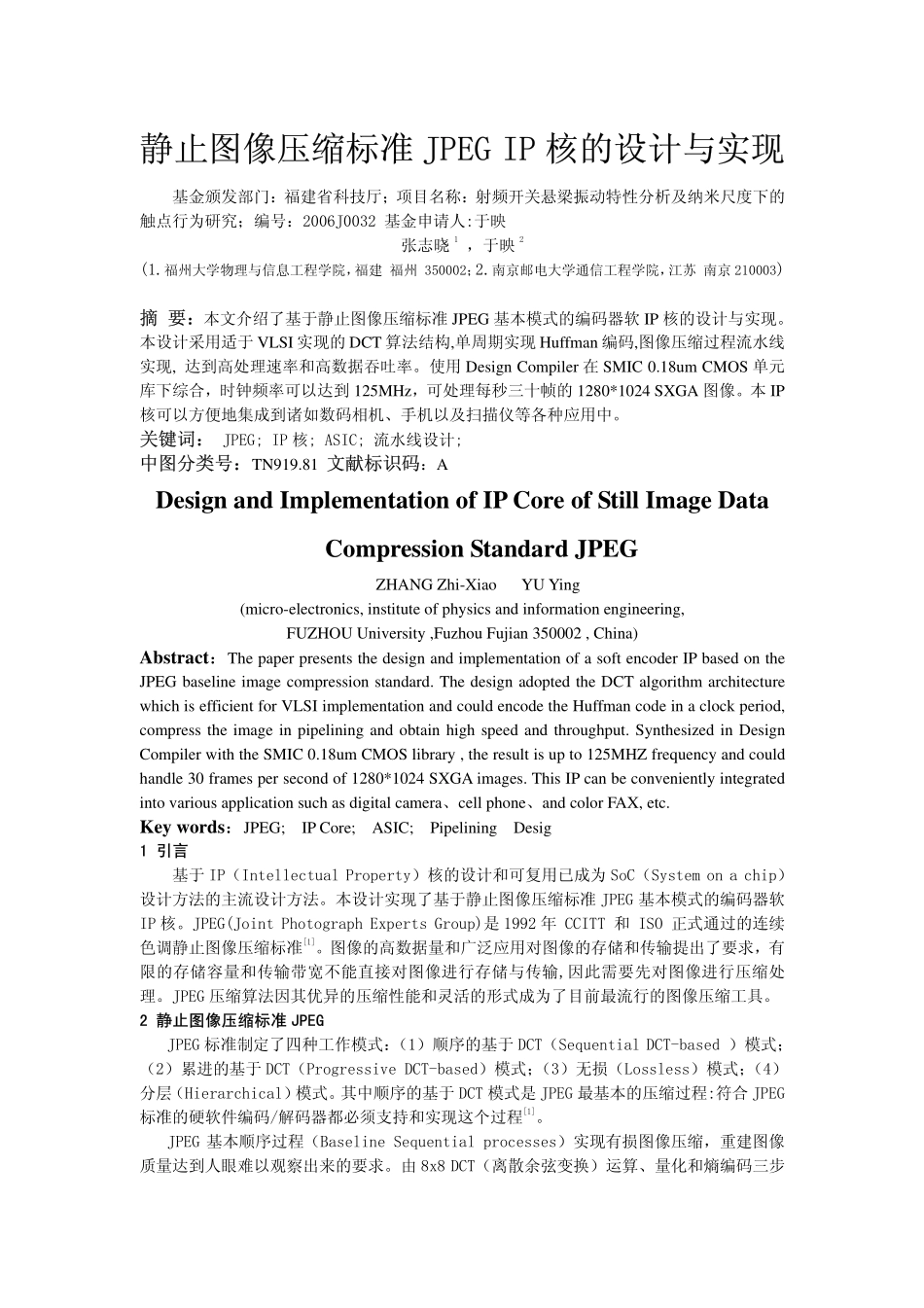

南京邮电大学通信工程学院,江苏南京210003)摘要:本文介绍了基于静止图像压缩标准JPEG基本模式的编码器软IP核的设计与实现

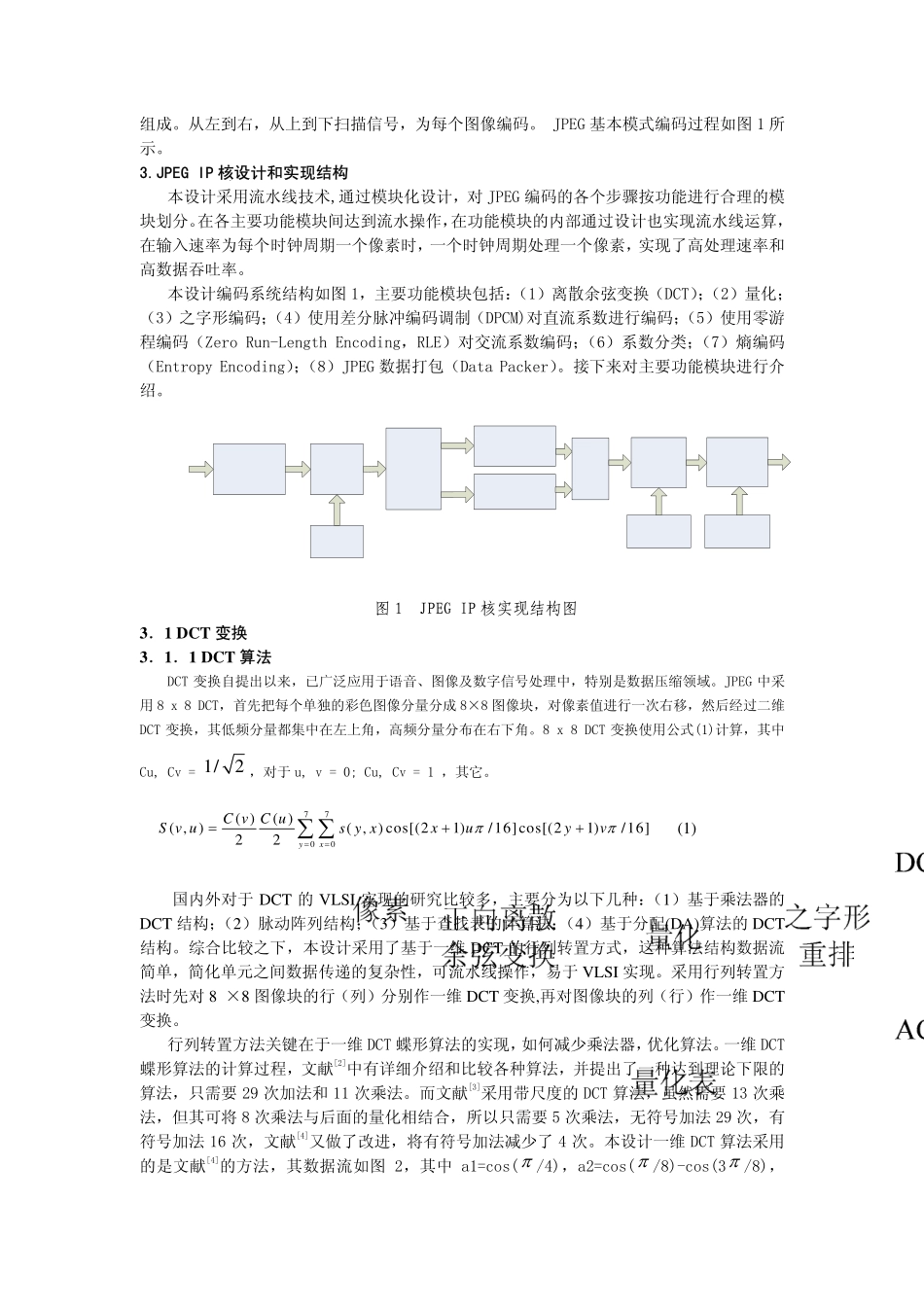

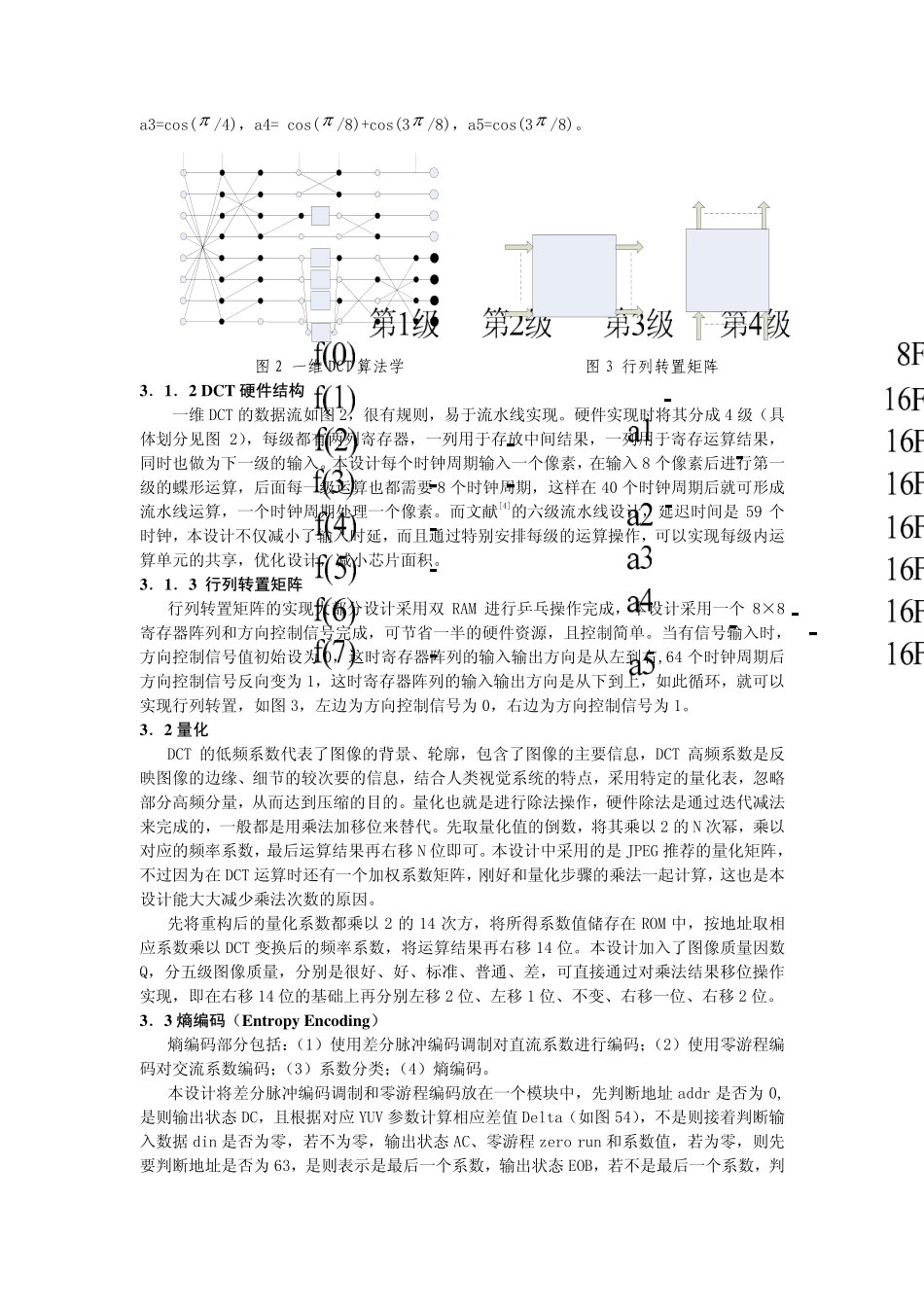

本设计采用适于VLSI实现的DCT算法结构,单周期实现Huffman编码,图像压缩过程流水线实现,达到高处理速率和高数据吞吐率

使用DesignCompiler在SMIC0

18umCMOS单元库下综合,时钟频率可以达到125MHz,可处理每秒三十帧的1280*1024SXGA图像

本IP核可以方便地集成到诸如数码相机、手机以及扫描仪等各种应用中

关键词:JPEG;IP核;ASIC;流水线设计;中图分类号:TN919

81文献标识码:ADesignandImplementationofIPCoreofStillImageDataCompressionStandardJPEGZHANGZhi-XiaoYUYing(micro-electronics,instituteofphysicsandinformationengineering,FUZHOUUniversity,FuzhouFujian350002,China)Abstract:ThepaperpresentsthedesignandimplementationofasoftencoderIPbasedontheJPEGbaselineimagecompressionstandard

ThedesignadoptedtheDCTalgorithmarchitecturewhichisefficientforVLSIimplementationand