射频锁相环基础理论环路的性能电路实解锁相环在手机中的应用一.基础理论锁相环路(PhaseLockedLoop)是一个闭环的相位控制系统,它的输出信号的相位能自动跟踪输入信号相位

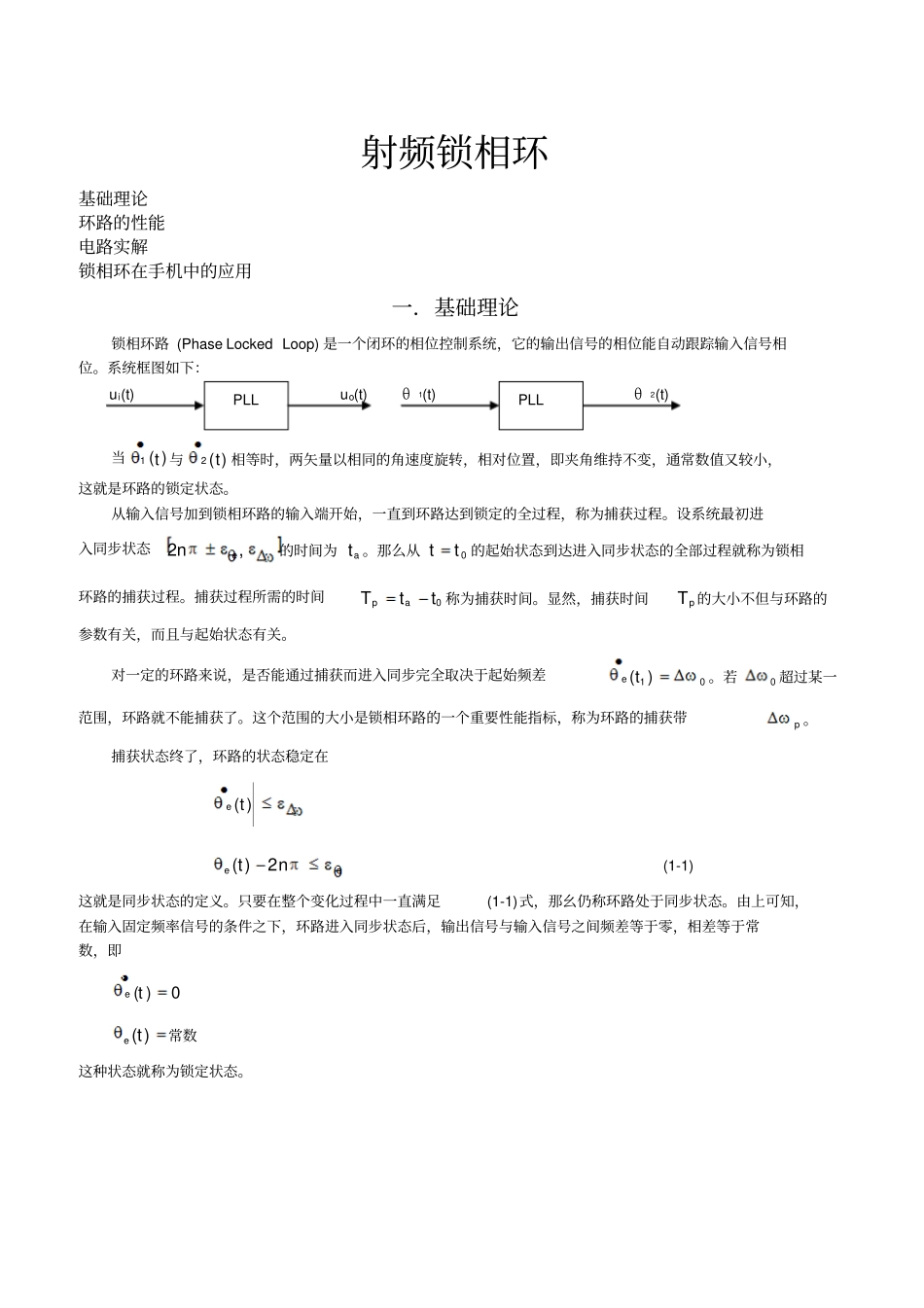

系统框图如下:ui(t)uo(t)θ1(t)θ2(t)当)(1t与)(2t相等时,两矢量以相同的角速度旋转,相对位置,即夹角维持不变,通常数值又较小,这就是环路的锁定状态

从输入信号加到锁相环路的输入端开始,一直到环路达到锁定的全过程,称为捕获过程

设系统最初进入同步状态,2en的时间为at

那么从0tt的起始状态到达进入同步状态的全部过程就称为锁相环路的捕获过程

捕获过程所需的时间0ttTap称为捕获时间

显然,捕获时间pT的大小不但与环路的参数有关,而且与起始状态有关

对一定的环路来说,是否能通过捕获而进入同步完全取决于起始频差01)(te

若0超过某一范围,环路就不能捕获了

这个范围的大小是锁相环路的一个重要性能指标,称为环路的捕获带p

捕获状态终了,环路的状态稳定在)(teeent2)((1-1)这就是同步状态的定义

只要在整个变化过程中一直满足(1-1)式,那幺仍称环路处于同步状态

由上可知,在输入固定频率信号的条件之下,环路进入同步状态后,输出信号与输入信号之间频差等于零,相差等于常数,即0)(te)(te常数这种状态就称为锁定状态

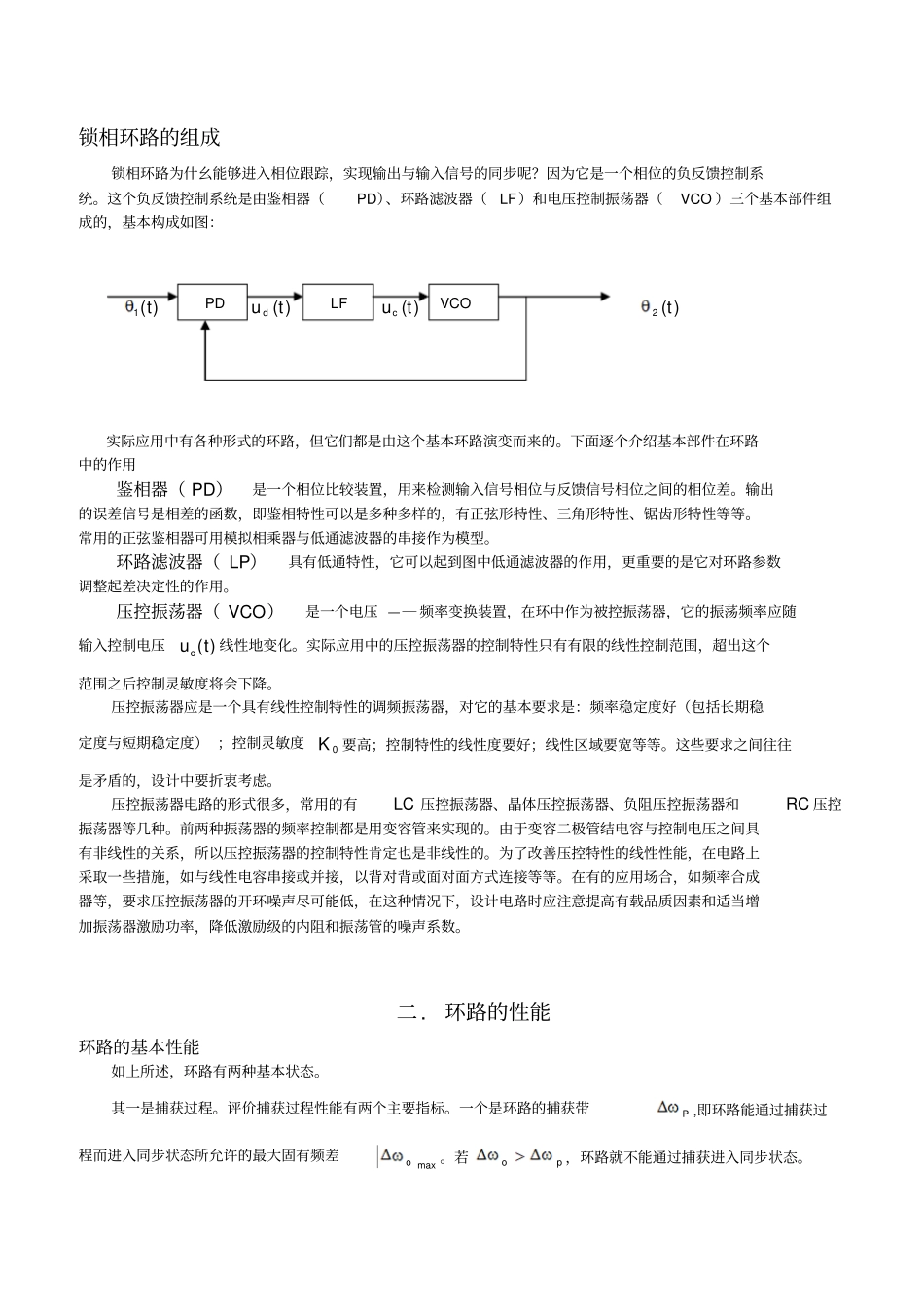

PLLPLL锁相环路的组成锁相环路为什幺能够进入相位跟踪,实现输出与输入信号的同步呢

因为它是一个相位的负反馈控制系统

这个负反馈控制系统是由鉴相器(PD)、环路滤波器(LF)和电压控制振荡器(VCO)三个基本部件组成的,基本构成如图:)(1t)(tud)(tuc)(2t实际应用中有各种形式的环路,但它们都是由这个基本环路演变而来的

下面逐个介绍基本部件在环路中的作用鉴相器(PD)是一个相位比较装置,用来检测输入信号相位与反馈信号相位之间的相位差