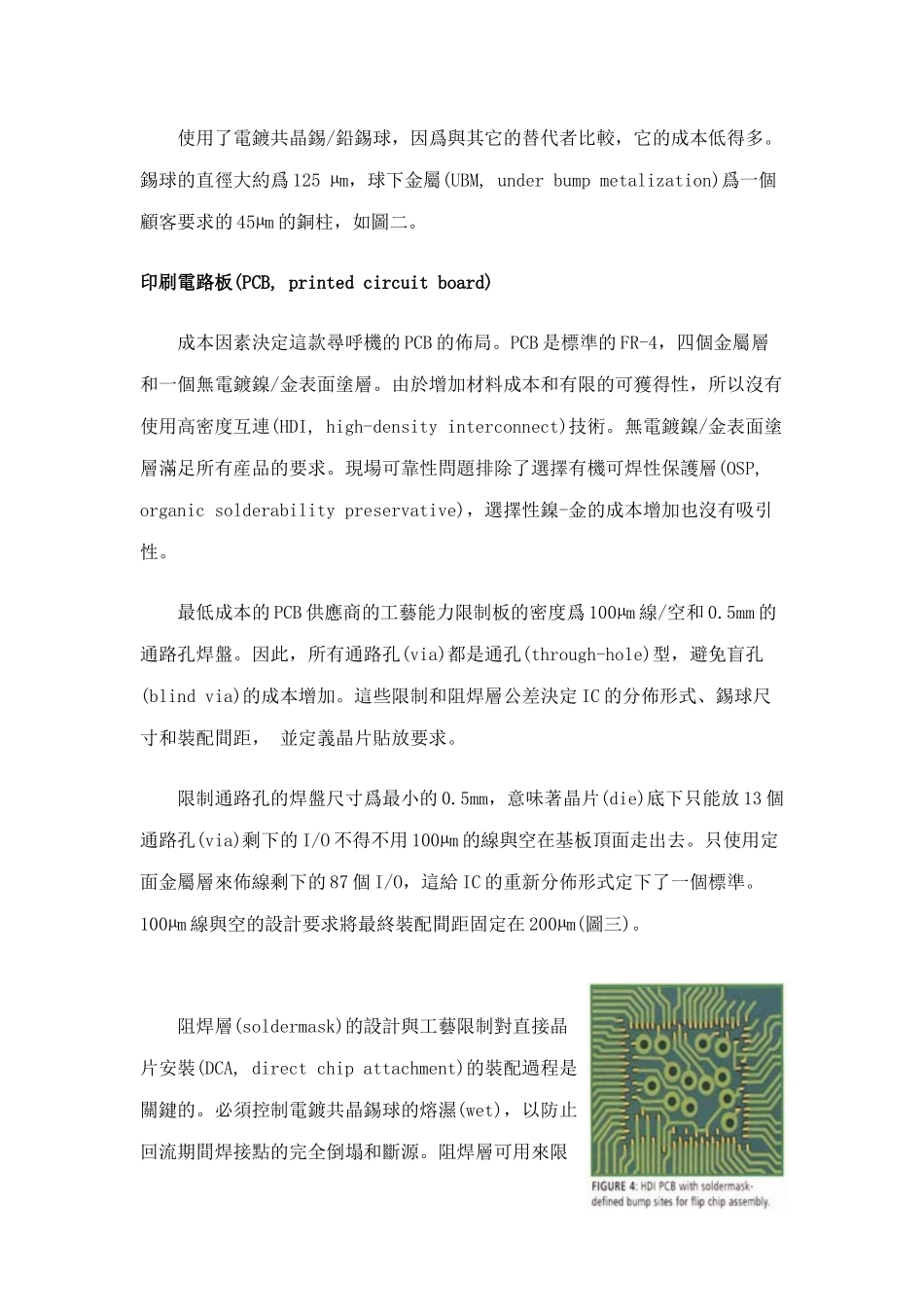

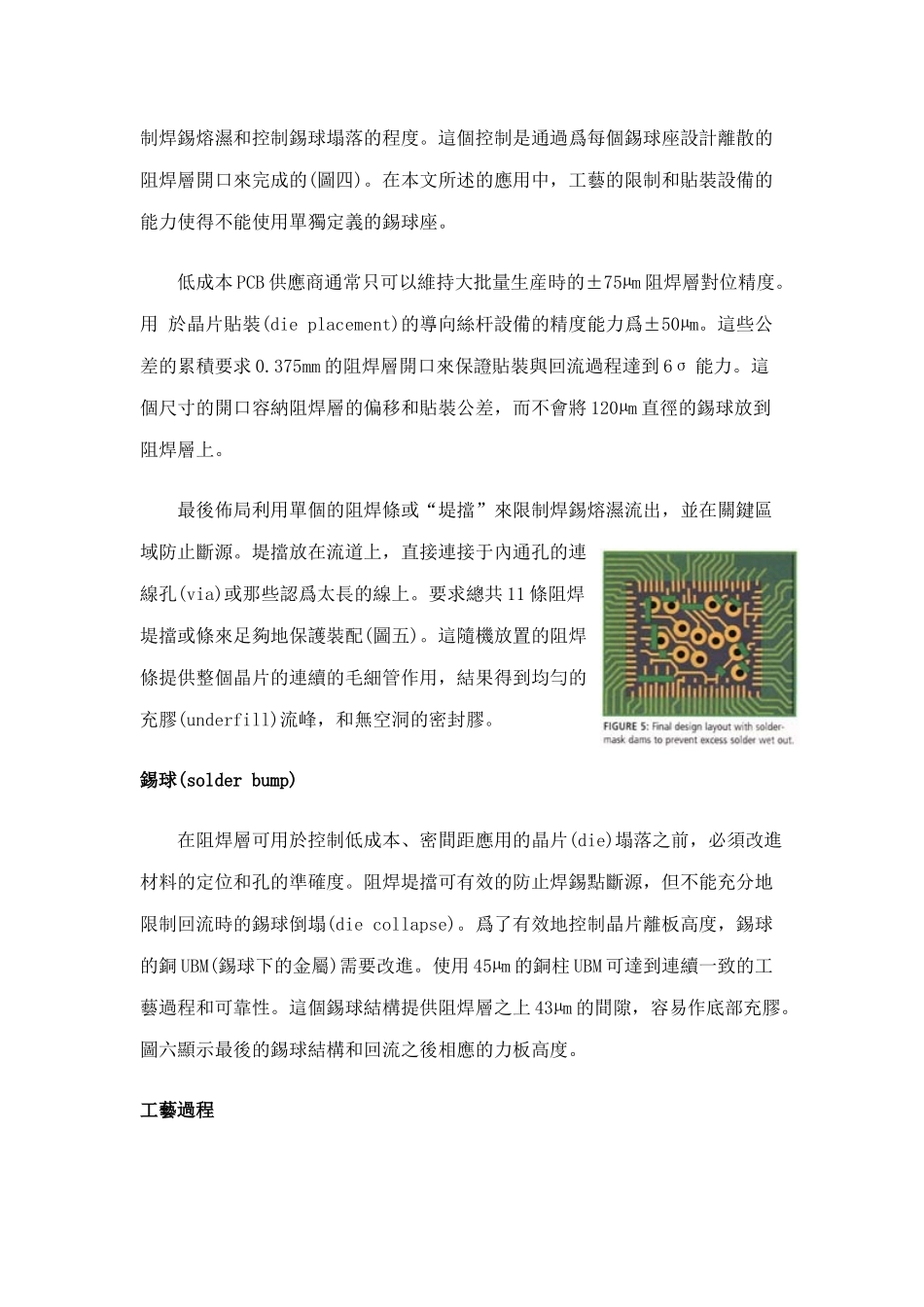

倒裝晶片:向主流製造工藝推進 By Dr. Scott Joslin, James Lance, Daniel Yeaple and Douglas Hendricks 創新的製造與設計技術使得成百萬使用倒裝晶片裝配的尋呼機成功地製造出來。 對較小外形和較多功能的低成本電子設備的需求繼續在增長。這些快速變化的市場挑戰著電子製造商,降低製造成本以保證可接受的利潤率。倒裝晶片裝配(flip chip assembly)被認爲是推進低成本、高密度攜帶型電子設備的製造所必須的一項技術。在低成本應用中,倒裝晶片的成功是因爲它可達到相對于傳統表面貼裝元件包裝更大的成本效益。例如,一款新的尋呼機利用了倒裝晶片技術將微控制器裝配於 PCB,因爲倒裝晶片使用較少的電路板空間,比傳統的塑膠球柵陣列(PBGA, plastic ball grid array)成本較低。材料積體電路(Integraded circuit)在這款尋呼機中的積體電路(IC, integrated circuit)是一個 5 x 5.6 mm 的微控制器,要求100 個輸入/輸出(I/O)連接於 PCB。將四周 I/O 重新分配爲 2.5 排減少點數(depopulated)的球柵陣列形式來接納 PCB 的線/空格以及通路孔焊盤的限制。錫球(bump)佈局與間距如圖一所示。 使用了電鍍共晶錫/鉛錫球,因爲與其它的替代者比較,它的成本低得多。錫球的直徑大約爲 125 µm,球下金屬(UBM, under bump metalization)爲一個顧客要求的 45µm 的銅柱,如圖二。印刷電路板(PCB, printed circuit board)成本因素決定這款尋呼機的 PCB 的佈局。PCB 是標準的 FR-4,四個金屬層和一個無電鍍鎳/金表面塗層。由於增加材料成本和有限的可獲得性,所以沒有使用高密度互連(HDI, high-density interconnect)技術。無電鍍鎳/金表面塗層滿足所有産品的要求。現場可靠性問題排除了選擇有機可焊性保護層(OSP, organic solderability preservative),選擇性鎳-金的成本增加也沒有吸引性。最低成本的 PCB 供應商的工藝能力限制板的密度爲 100µm 線/空和 0.5mm 的通路孔焊盤。因此,所有通路孔(via)都是通孔(through-hole)型,避免盲孔(blind via)的成本增加。這些限制和阻焊層公差決定 IC 的分佈形式、錫球尺寸和裝配間距, 並定義晶片貼放要求。限制通路孔的焊盤尺寸爲最小的 0.5mm,意味著晶片(die)底下只能放 13 個通路孔(via)剩下的 I/O 不得不用 100µm 的線與空在基板頂面走出去。只使用定面金屬層來佈線剩下的 87 個 I/O,這給 IC 的重新分佈形式定下了一個標準。100µ...