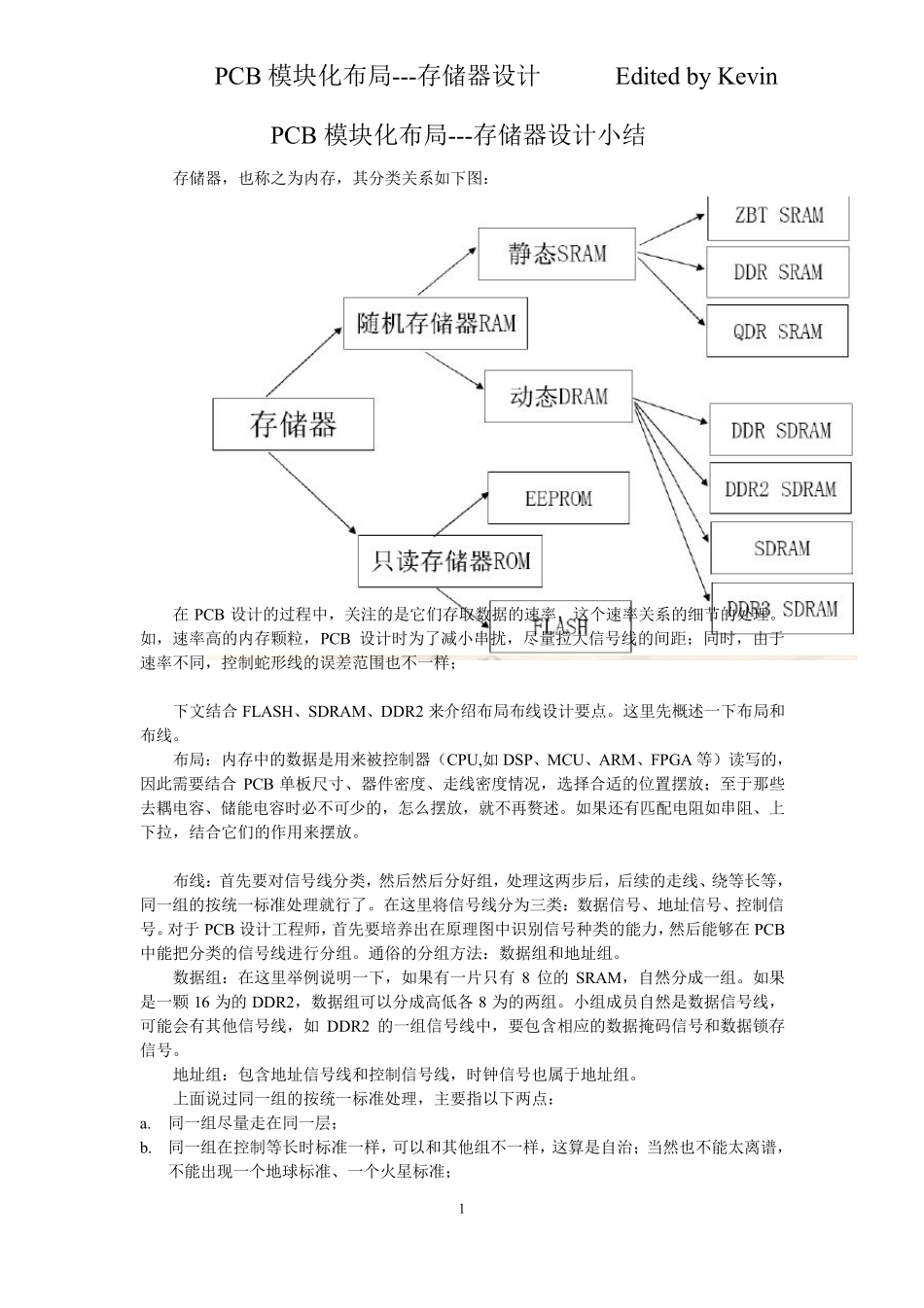

PCB 模块化布局---存储器设计 Edited by Kevin 1 PCB 模块化布局---存储器设计小结 存储器,也称之为内存,其分类关系如下图: 在PCB 设计的过程中,关注的是它们存取数据的速率,这个速率关系的细节的处理

如,速率高的内存颗粒,PCB 设计时为了减小串扰,尽量拉大信号线的间距;同时,由于速率不同,控制蛇形线的误差范围也不一样; 下文结合FLASH、SDRAM、DDR2 来介绍布局布线设计要点

这里先概述一下布局和布线

布局:内存中的数据是用来被控制器(CPU,如DSP、MCU、ARM、FPGA 等)读写的,因此需要结合PCB 单板尺寸、器件密度、走线密度情况,选择合适的位置摆放;至于那些去耦电容、储能电容时必不可少的,怎么摆放,就不再赘述

如果还有匹配电阻如串阻、上下拉,结合它们的作用来摆放

布线:首先要对信号线分类,然后然后分好组,处理这两步后,后续的走线、绕等长等,同一组的按统一标准处理就行了

在这里将信号线分为三类:数据信号、地址信号、控制信号

对于PCB 设计工程师,首先要培养出在原理图中识别信号种类的能力,然后能够在PCB中能把分类的信号线进行分组

通俗的分组方法:数据组和地址组

数据组:在这里举例说明一下,如果有一片只有 8 位的SRAM,自然分成一组

如果是一颗16 为的DDR2,数据组可以分成高低各 8 为的两组

小组成员自然是数据信号线,可能会有其他信号线,如DDR2 的一组信号线中,要包含相应的数据掩码信号和数据锁存信号

地址组:包含地址信号线和控制信号线,时钟信号也属于地址组

上面说过同一组的按统一标准处理,主要指以下两点: a

同一组尽量走在同一层; b

同一组在控制等长时标准一样,可以和其他组不一样,这算是自治;当然也不能太离谱,不能出现一个地球标准、一个火星标准; PCB 模块化布局---存储器设计 Edi