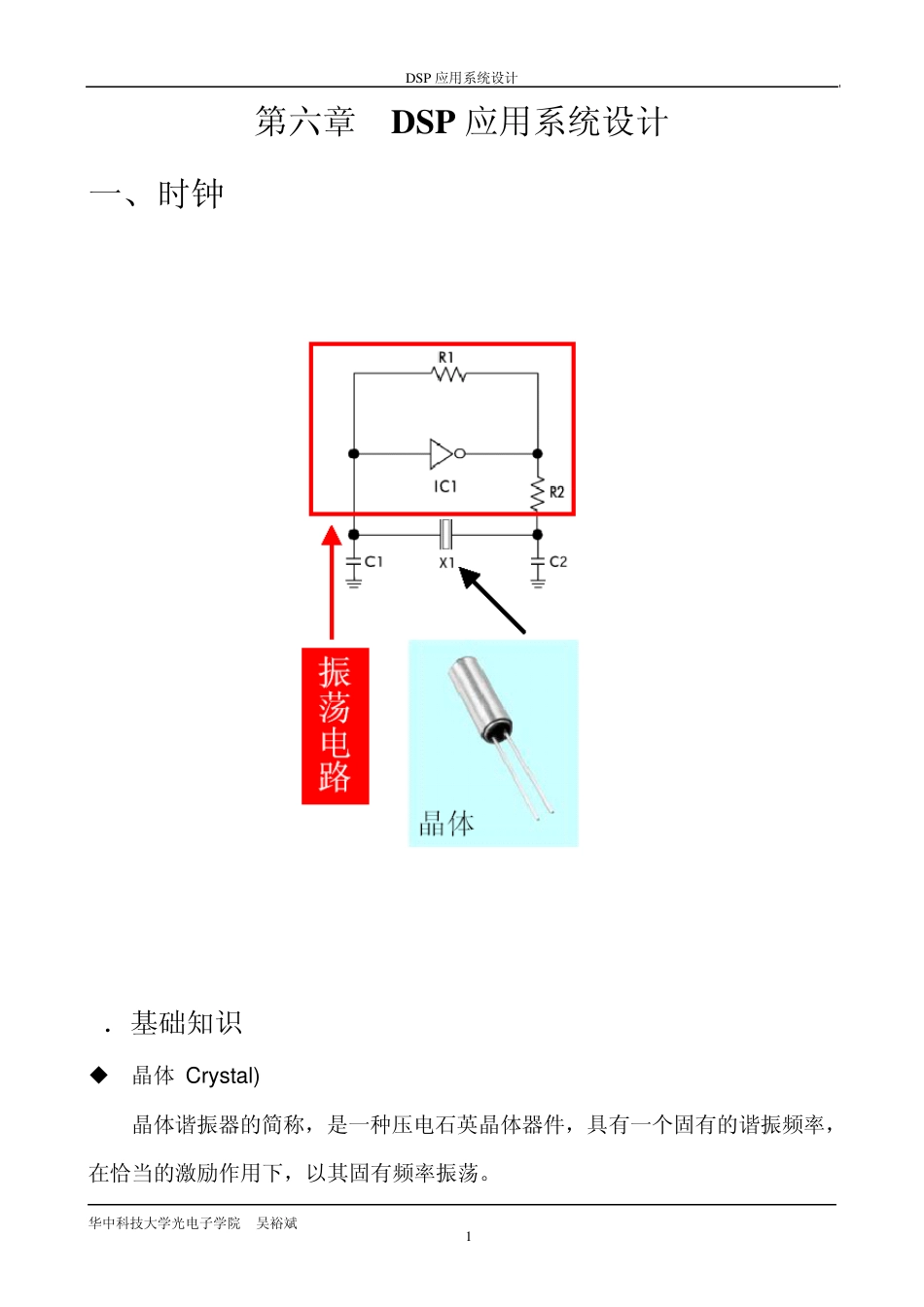

DSP应用系统设计 华中科技大学光电子学院 吴裕斌 1 第六章 DSP 应用系统设计 一、时钟 1.基础知识 晶体(Cry stal) 晶体谐振器的简称,是一种压电石英晶体器件,具有一个固有的谐振频率,在恰当的激励作用下,以其固有频率振荡。 DSP应用系统设计 华中科技大学光电子学院 吴裕斌 2 振荡电路(Oscillator) 为晶体提供激励和检测的电路 晶振(Crystal Oscillator) 将晶体、振荡器和负载电容集成在一起,其输出直接为一方波时钟信号。 锁相环电路PLL(Phase-Locked Loops) 用于对输入时钟信号进行分频或倍频的电路晶体 2.哪些器件需要时钟 DSP CPU时钟 EMIF时钟(仅C55x和C6000系列DSP) 串行通信器件 UART USB „„ 音频/视频器件 Audio Codec器件 Video Decoder和Encoder器件 „„ 3.器件的时钟选项 大多数器件片内均包含振荡电路,只需外加晶体和2个负载电容即可产生所需的时钟信号。也可禁止片内振荡电路,直接由外部提供时钟信号 TI DSP更提供多种灵活的时钟选项: DSP应用系统设计 华中科技大学光电子学院 吴裕斌 3 片内/片外振荡器 片内PLL PLL分频/倍频系数可由硬件/软件配置 不同的DSP时钟可配置的能力可能不同,使用前应参考各自的数据手册 4.时钟电路 a.由晶体+内部振荡器 产生 Internal Oscillator 优点: 电路简单:只需晶体+2个电容 价格便宜,占地小 时钟信号电平自然满足要求 缺点: 驱动能力差,不能同时供给其他器件使用 频率范围小:20KHz~60MHz 注意事项: 负载电容:配置正确的负载电容 C6000、C5510等DSP无OSC b.由晶振(Oscillator)产生 优点: 电路简单 占地小 频率范围宽:1MHz~400MHz DSP应用系统设计 华中科技大学光电子学院 吴裕斌 4 驱动能力强:可提供多个器件使用 缺点: 成本较高 频率生产时已确定,多个独立的时钟需要多个晶振 注意事项: 使用时要注意时钟信号电平,一般为5V或3.3V,要求1.8V电平的时钟不能选用,如VC5401、VC5402、VC5409和F281x c.由可编程时钟芯片产生 优点: 电路简单、占地小:可编程时钟芯片+晶体+2个外部电容 多个时钟输出,可产生特殊的频率值,适合于多时钟源的系统 驱动能力强:可提供多个器件使...