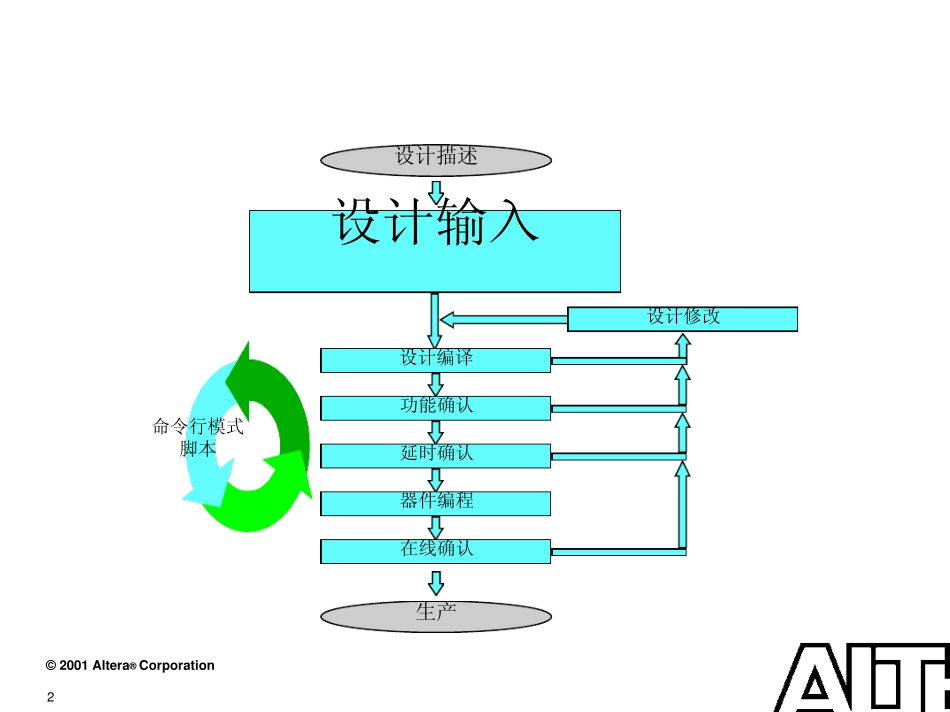

Qu artu sII 使用说明 © 2001 Altera® Corporation2生产设计描述设计编译功能确认延时确认器件编程在线确认设计修改设计输入命令行模式脚本© 2001 Altera® Corporation3设计输入

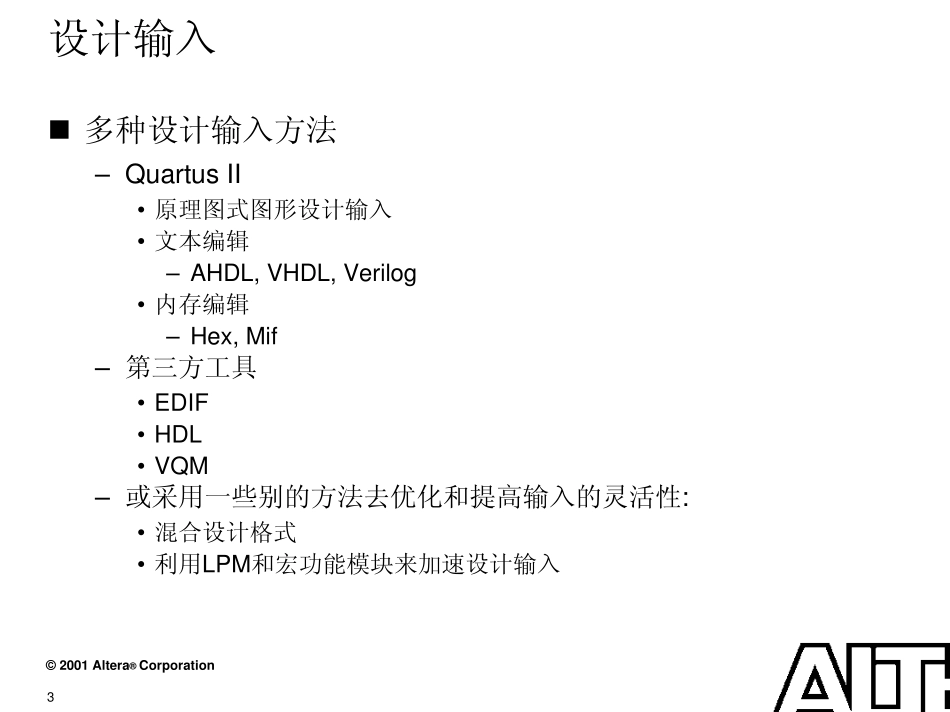

多种设计输入方法– Quartus II• 原理图式图形设计输入• 文本编辑– AHDL, VHDL, Verilog• 内存编辑– Hex, Mif– 第三方工具• EDIF• HDL• VQM– 或采用一些别的方法去优化和提高输入的灵活性:• 混合设计格式• 利用LPM和宏功能模块来加速设计输入© 2001 Altera® Corporation4Quartus II内存编辑Quartus II文本编辑Quartus II模块编辑顶层文件

gdf顶层文件的扩展名可以是:bdf,

edif or

vhdBlock文件Symbol文件Text文件Text文件

vText文件从第三方工具输入Exemplar,Synopsys,Synplicity,etc

由 Quartus II 产生VHDL原理图原理图

tdfText文件AHDLVerilog

edifText文件

vhdl, vqmMegaWizard®Manager设计输入文件© 2001 Altera® Corporation5图表和原理图编辑器该编辑器既可以编辑图表模块,又可以编辑原理图

图表模块编辑是主要的顶层设计的主要方法

原理图编辑是传统的设计输入方法

用户可以利用加入Quartus II 提供的LPMs,宏功能等涵数以及用户自己的库涵数来设计

提供“智能”的模块链接和映射© 2001 Altera® Corporation6图表模块 –设计流