《计算机组成原理》 实验报告 (2019-2020 学年 第一学期) 项目名称: 静态随机存储器 实验序号: 02 专 业: 计算机科学与技术 班 级: 18 计算机卓越1 班 姓 名: ZRZ 学 号: 1810716643 指导教师: 许高攀 成 绩: 计算机与信息工程学院 2 01 9 年 1 1 月 4 日 1 实验目的及要求 掌握静态随机存储器RAM 工作特性及数据的读写方法

2 实验设备(环境)及要求 PC 机一台,TD-CMA 实验系统一套

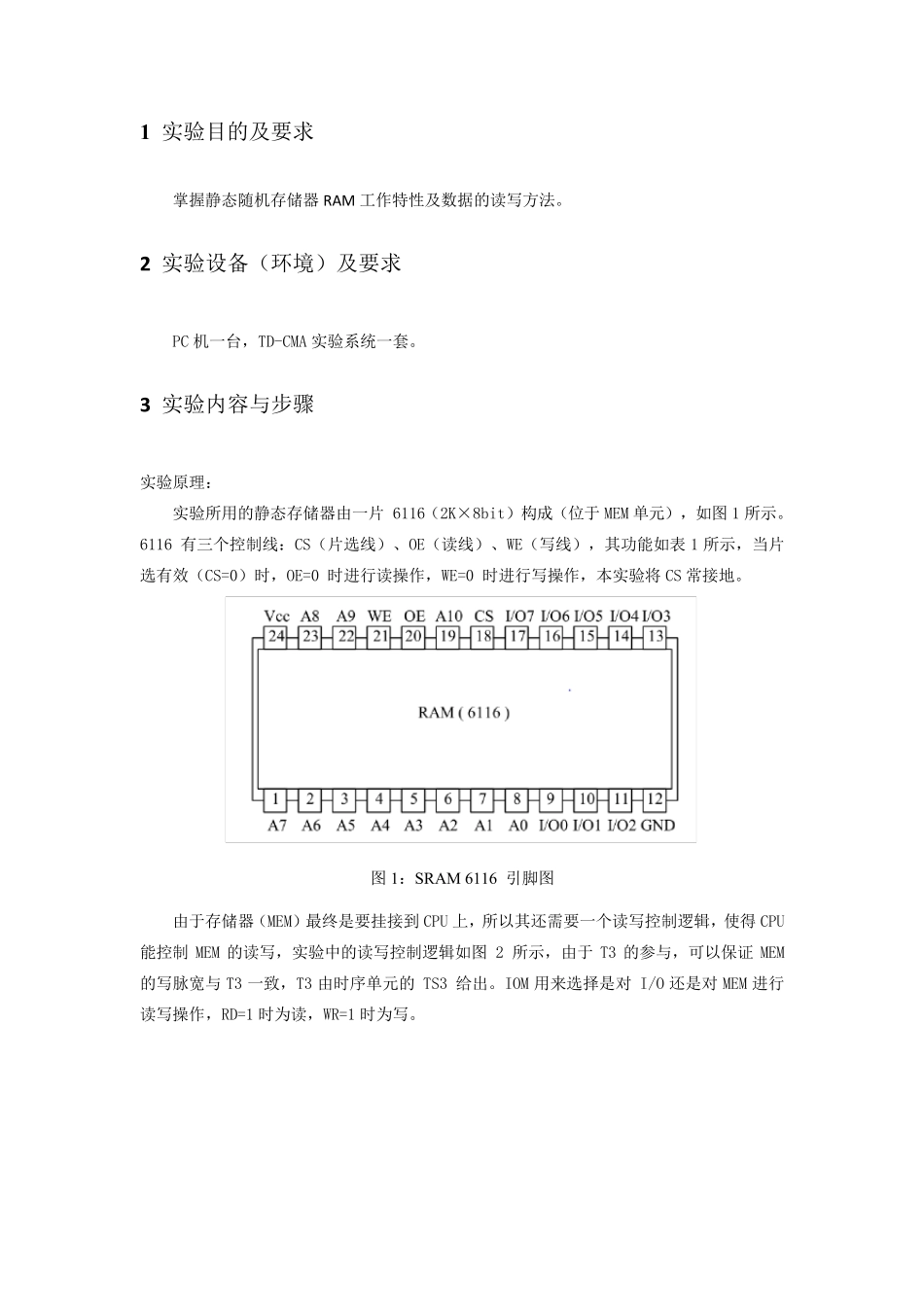

3 实验内容与步骤 实验原理: 实验所用的静态存储器由一片 6116(2K×8bit)构成(位于MEM 单元),如图1 所示

6116 有三个控制线:CS(片选线)、OE(读线)、WE(写线),其功能如表1 所示,当片选有效(CS=0)时,OE=0 时进行读操作,WE=0 时进行写操作,本实验将CS 常接地

图1:SRAM 6116 引脚图 由于存储器(MEM)最终是要挂接到CPU 上,所以其还需要一个读写控制逻辑,使得CPU能控制MEM 的读写,实验中的读写控制逻辑如图 2 所示,由于T3 的参与,可以保证MEM的写脉宽与T3 一致,T3 由时序单元的 TS3 给出

IOM 用来选择是对 I/O 还是对MEM 进行读写操作,RD=1 时为读,WR=1 时为写

表1:SRAM 6116 功能表 CS’ WE’ OE’ 功能 1 X X 不选择 0 1 0 读 0 0 1 写 0 0 0 写 图2:读写控制逻辑 实验原理图如图3 所示,存储器数据线接至数据总线,数据总线上接有8 个LED 灯显示D7…D0 的内容

地址线接至地址总线,地址总线上接有8 个LED 灯显示A7…A0 的内容,地址由地址锁存器(74LS273,位于PC&AR 单元)给出

数据开关(位于IN 单元)经一个三态门(74LS245)连至数据总线,