SHANGHAI UNIVERSITY 数字电子技术课程实践项目 学 院 机电工程与自动化学院 专 业 电气工程及其自动化 班 级 电气 7 班 学 号 ******** 姓 名 孟蔓菁 用下降沿触发的JK-FF 组成四位同步加计数器、异步加计数器 一、 下降沿触发的 JK -FF 组成四位同步加计数器 同步加计数器:同步计数器中,所有触发器的 CP 端是相连的,CP的每一个触发沿都会使所有的触发器状态更新

实验电路图: 实验原理:同步计数器中各触发器的 CP端输入同一时钟脉冲,因此触发器的翻转状态就由它们的输入信号 J、K 端的状态决定

1、 时钟方程 CP0=CP1=CP2=CP3=CP 2

驱动方程 3

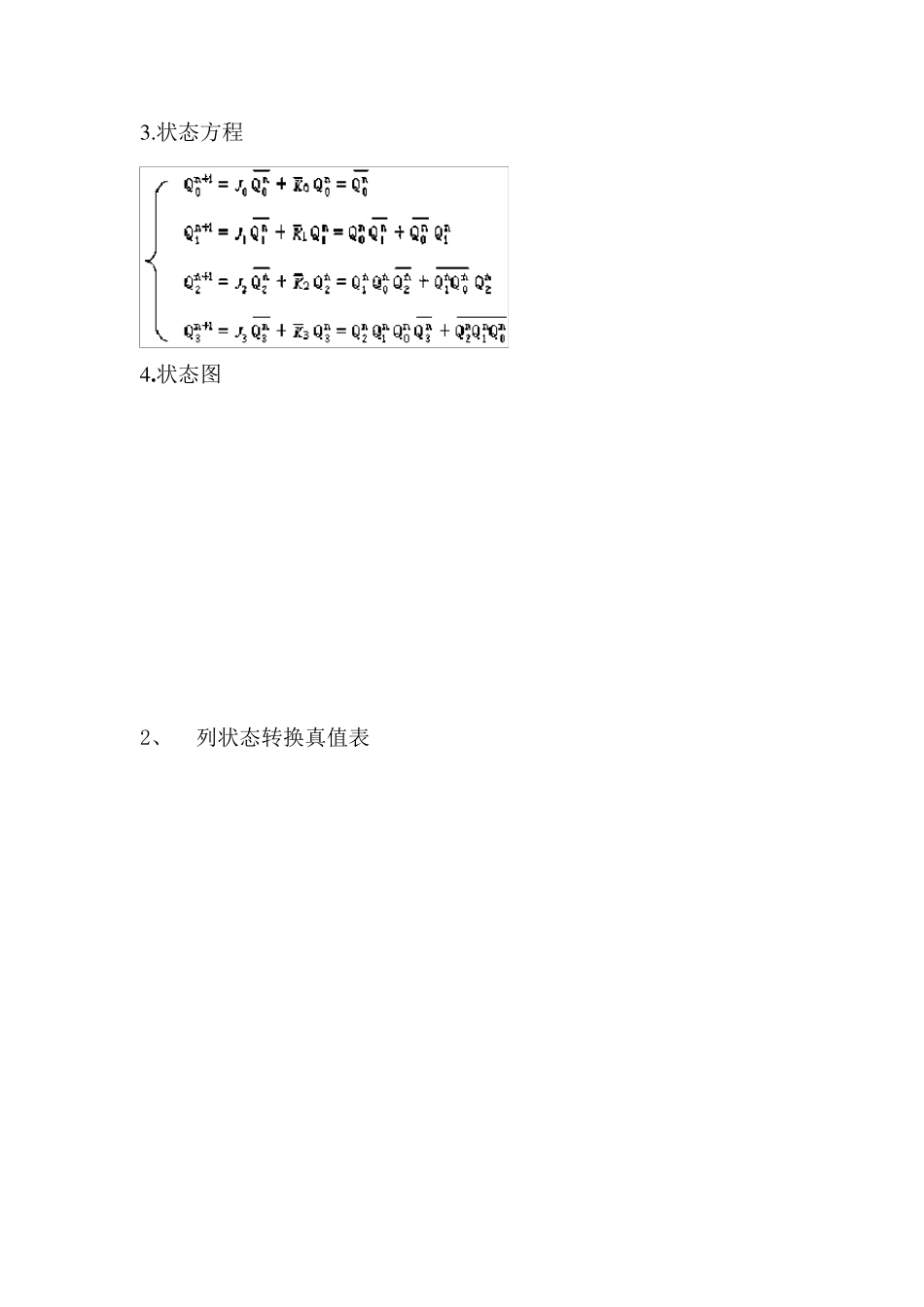

状态方程 4

状态图 2、 列状态转换真值表 6

理论波形图 7

实验波形图 Q 0 波形: Q 1 波形 Q 2 波形 Q 3 波形 二、 下降沿触发的 JK -FF 组成四位异步加计数器 异步计数器是在做加 1 计数时是采取从低位到高位逐位进位的方式工作的

因此其中的各个触发器不是同步翻转的

按照二进制加法计数规则,每一位如果已经是1,则再计入1 时应变为0,同时向高位发出进位信号,使高位翻转

实验电路图: 1、时钟信号 CP0=CP CP1=Q 0 CP2=Q 1 CP3=Q 2 2、驱动方程 J 0=K0= J1=K1= J2=K2= J3=K3=1 3、状态方程 3、 真值表 每16 个 CP循环一周 5、理论波形图 6、实际波形图 Q 0 波形 Q 1 波形 Q 2 波形 Q 3 波形