中国科学技术大学·微纳电子系统集成研究中心 数模混合电路设计流程 - 1 / 21 - 数 模 混 合电路设计流程 马昭鑫 2012/5/23 本文主要面向模拟电路设计者,讲解了从行为级代码形式的数字电路到数模混合版图之间的流程,默认模拟版图和数字电路的行为级代码、testbench 已经完成

阅读者需确定自己会编写Verilog 或 Spice 格式的网表,熟悉 Linux 的文件操作,了解 Spectre、Virtuoso、Calibre、Modelsim、Design Compiler(dc)、Astro 等 EDA 工具的使用方法

由于本人才疏学浅,经验不足,难免会在文中出现一些错误,恳请高手给予指正

数模混合电路的仿真方法 一般的设计流程中数字电路和模拟电路是分开进行设计的,但有些时候希望能将数字电路和模拟电路放在一起仿真来验证设计,这就需要用到混合电路的仿真方法

在 Cadence工具中有专门用作混合电路仿真的仿真器spectreVerilog,其实现方法是首先将模拟模块与数字模块区分开并设置接口电平,然后在 ADE 中设置数字电路的测试代码,调用不同的仿真器分别对 数字模块和模拟模块进行仿真,最 后将结 果 汇 总 显 示 或输 出

下 面将以 一个 简 单 实例 的形式讲解混合电路的仿真方法

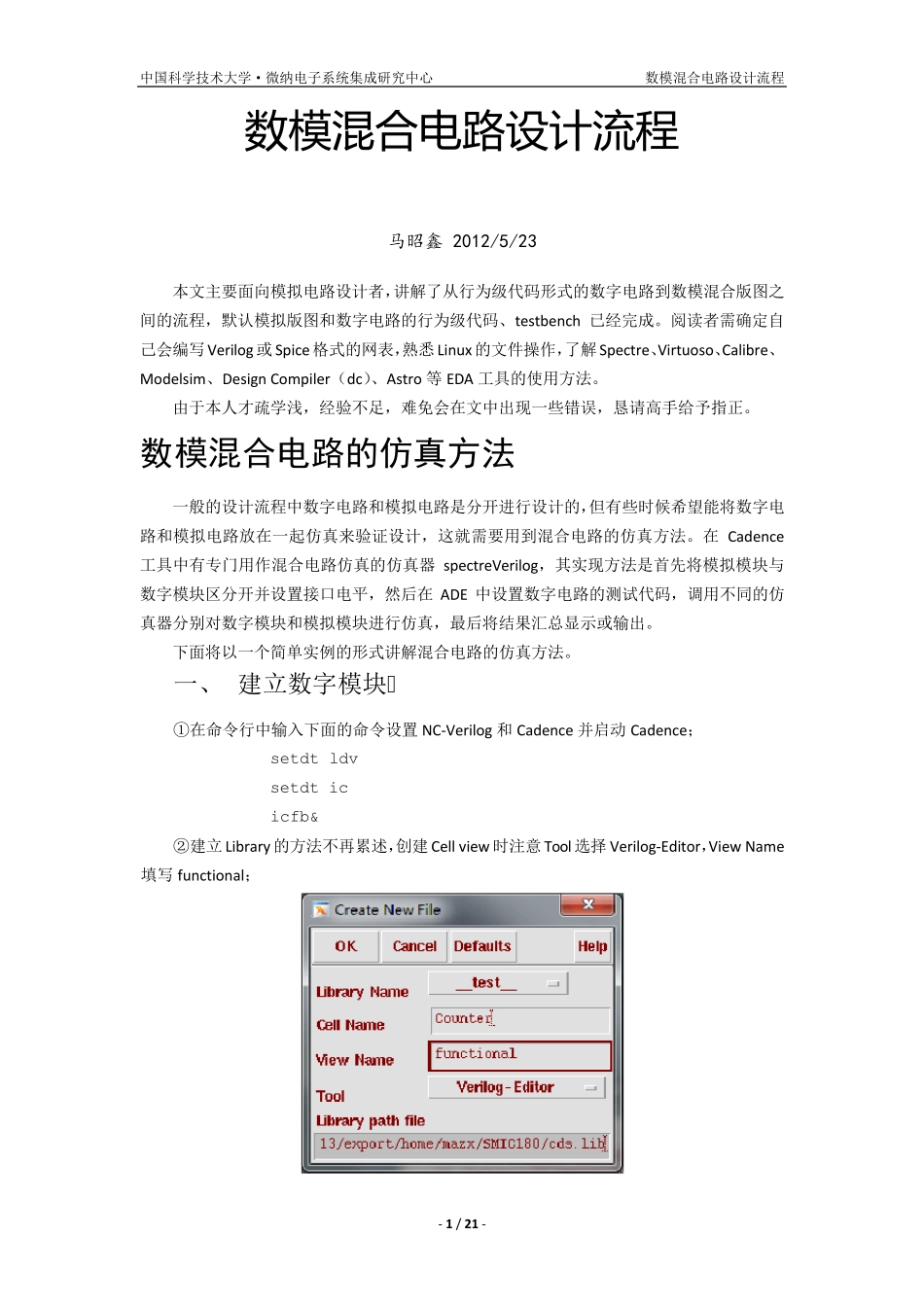

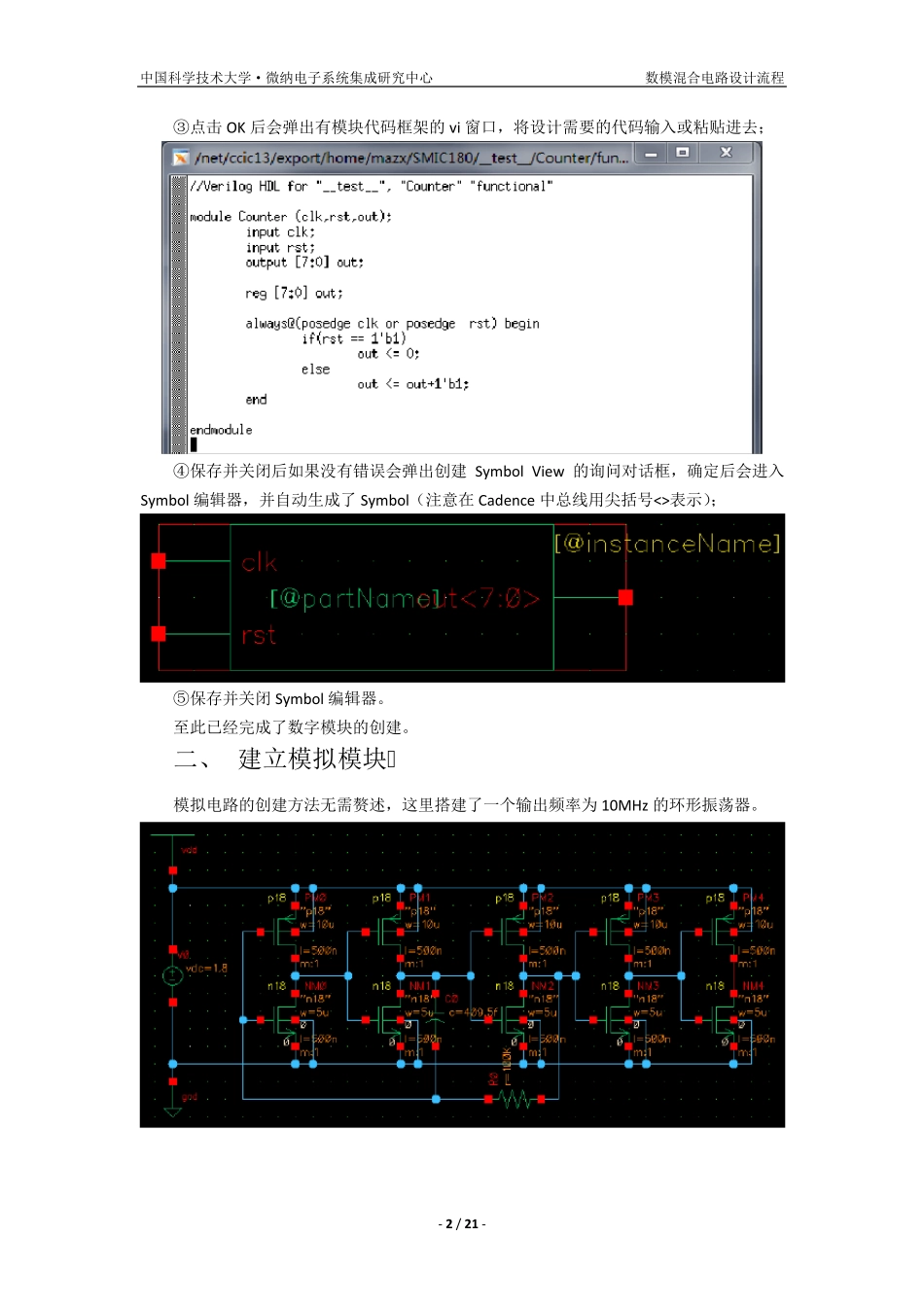

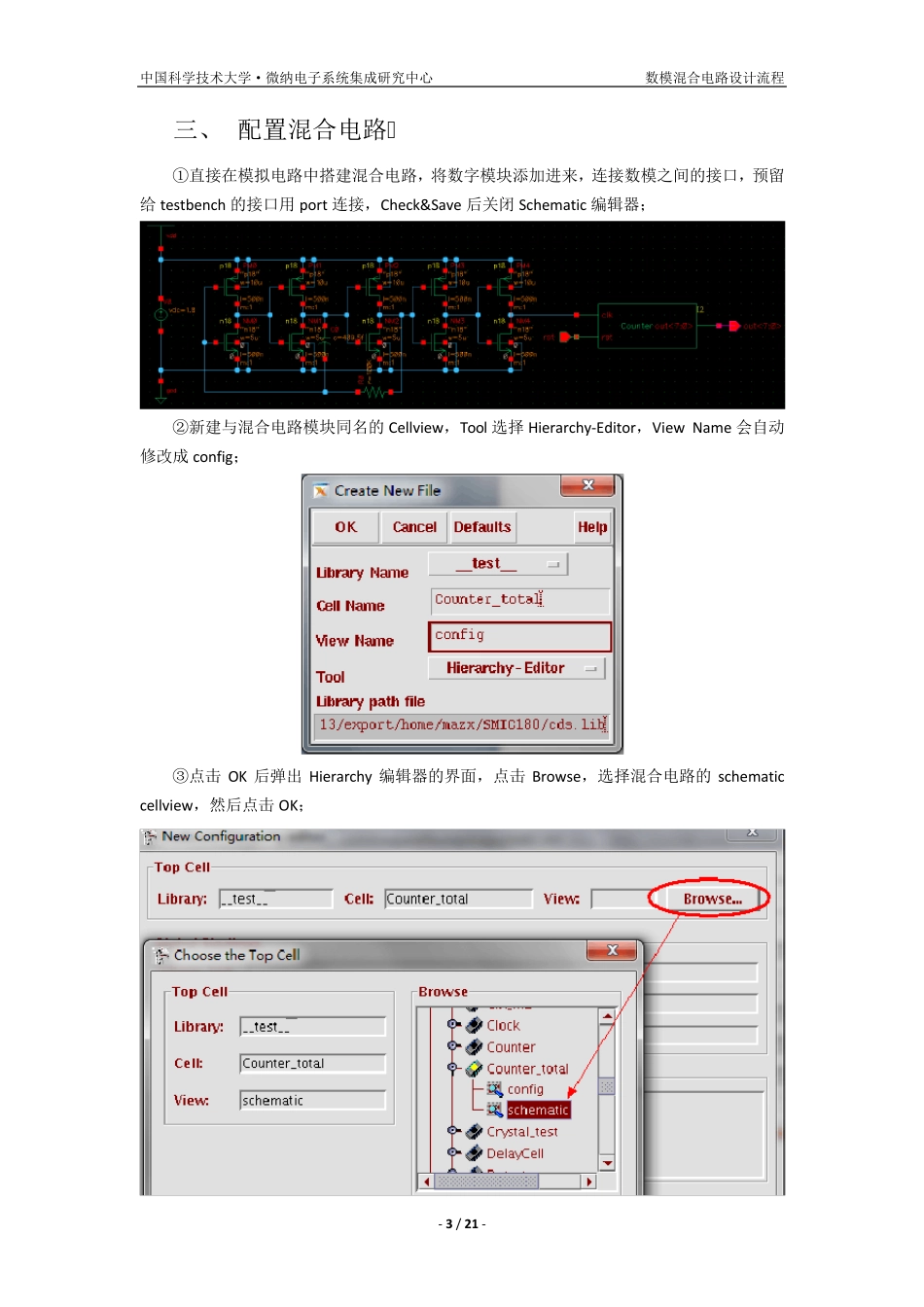

一、 建 立 数字模块 ① 在命 令 行中输 入 下 面的命 令 设置NC-Verilog 和 Cadence 并启 动 Cadence; setdt ldv setdt ic icfb& ② 建 立 Library 的方法不再 累 述 ,创 建 Cell view 时注 意 Tool 选 择 Verilog-Editor,View Name填 写 functional; 中国科学技术大学·微纳电子系统集成研究中心 数模混合电路设计流程 - 2 / 21 - ③