1 基于Mu ltisim 数字电路仿真实验 一、实验目的 1

掌握虚拟仪器库中关于测试数字电路仪器的使用方法,入网数字信号发生器和逻辑分析仪的使用

进一步了解 Multisim 仿真软件基本操作和分析方法

二、实验内容 用数字信号发生器和逻辑分析仪测试 74LS138 译码器逻辑功能

三、实验原理 实验原理图如图所示: 四、实验步骤 1

在 Multisim 软件中选择逻辑分析仪,字发生器和 74LS138 译码器; 2

数字信号发生器接 138 译码器地址端,逻辑分析仪接 138 译码器输出端

并按规定连好译码器的其他端口

点击字发生器,控制方式为循环,设置为加计数,频率设为 1KHz,并设置显 2 示为二进制;点击逻辑分析仪设置频率为1KHz

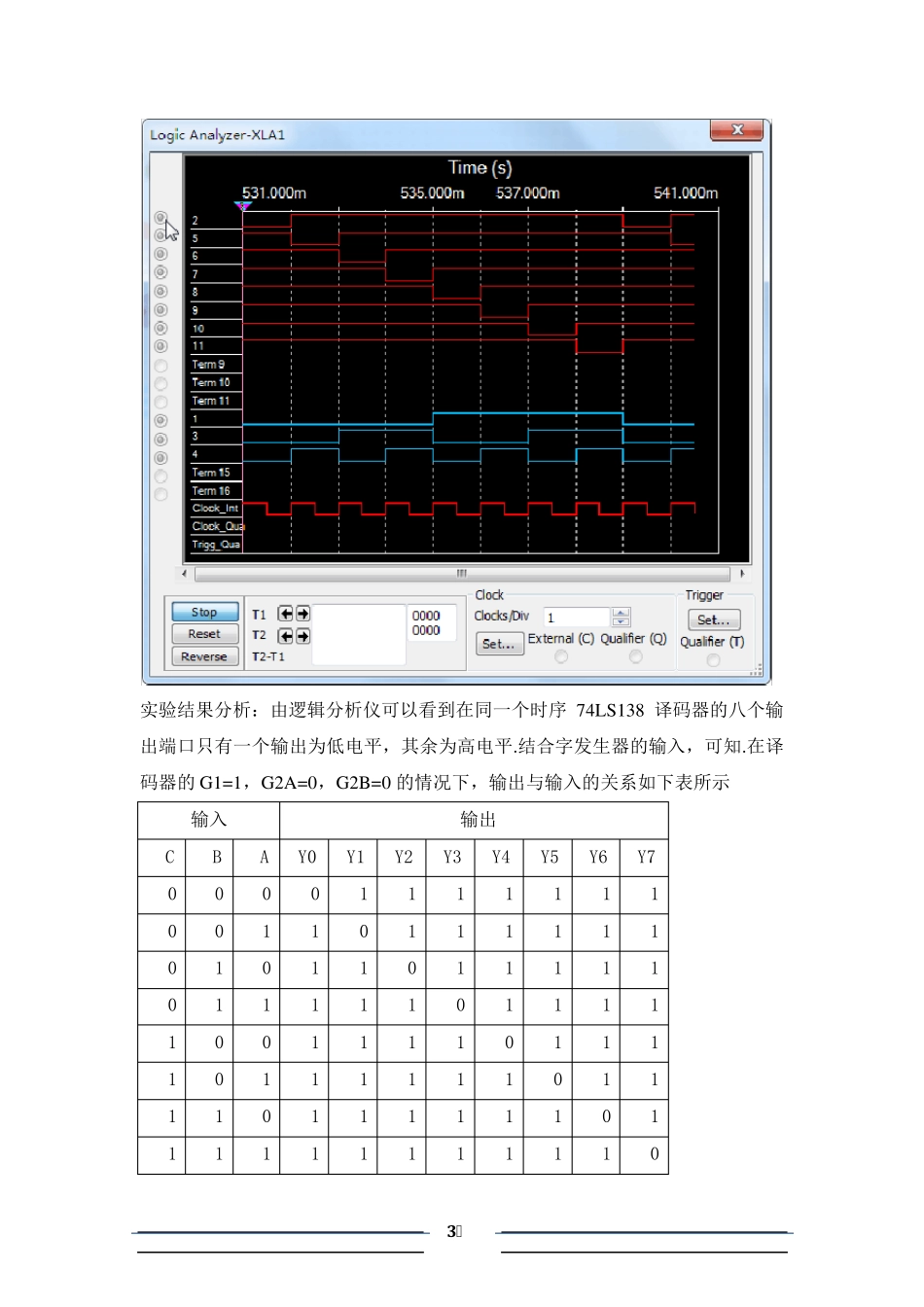

相关设置如下图 五、实验数据及结果 逻辑分析仪显示图下图 3 实验结果分析:由逻辑分析仪可以看到在同一个时序 74LS138 译码器的八个输出端口只有一个输出为低电平,其余为高电平

结合字发生器的输入,可知

在译码器的 G1=1,G2A=0,G2B=0 的情况下,输出与输入的关系如下表所示 输入 输出 C B A Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 0 0 0 0 1 1 1 1 1 1 1 0 0 1 1 0 1 1 1 1 1 1 0 1 0 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0 0 1 1 1 1 0 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 0 4 当G1=1,G2A=0,G2B=0 中任何一个输入不满足时,八个输出都为1 六、实验总结 通过本次实验,对 Mu ltisim 的基本操作方法有了一个简单的了解

同时分析了 38 译码器的功能,结果与我们