Cadence 的数模混合仿真工具spectraverilog 能够实现数字模拟电路联仿的功能,对于模拟电路的输入信号可以利用数字接口很方便的进行设置

主要用来进行功能仿真

步骤: 1. 准备 schematic,如电路单元 mix 2. 从库管理器中建立 mix单元的config view

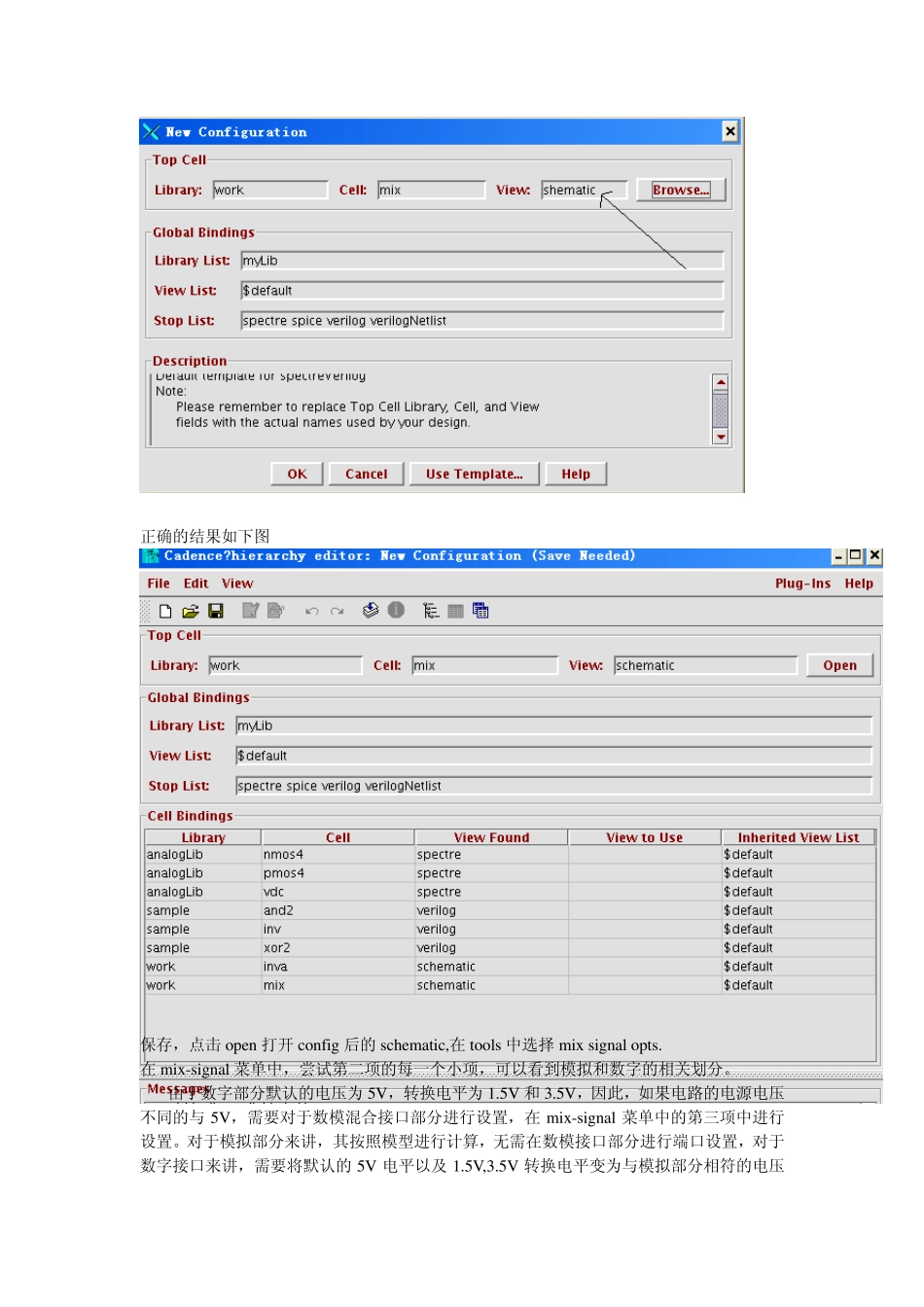

在 use template 中选择 spectraverilog,然后 ok 将 top cell 中的myview 改为实际的schemtic,然后 ok 正确的结果如下图 保存,点击open 打开config 后的schematic,在tools 中选择mix signal opts

在mix -signal 菜单中,尝试第二项的每一个小项,可以看到模拟和数字的相关划分

由于数字部分默认的电压为 5V,转换电平为 1

5V,因此,如果电路的电源电压不同的与 5V,需要对于数模混合接口部分进行设置,在mix -signal 菜单中的第三项中进行设置

对于模拟部分来讲,其按照模型进行计算,无需在数模接口部分进行端口设置,对于数字接口来讲,需要将默认的5V 电平以及 1

5V 转换电平变为与模拟部分相符的电压值,比如电源3V ,转换电平为1

设置如下, 对于与模拟器件相连接的数字输出端,将高电平由 5V 改为3V 对于与模拟器件相连接的数字输入端,将转换电平由 1

5V 改为3

5V 改为1V 和2V 所有数模混合接口的相关的数字端口都需要改动,如下图所示的数模接口部分 3. 调出 analog 仿真工具,并设置为 spectrev erilog 4 . 编写端口的输入激励文件 设置传输分析的时间长度 5. 其余步骤同模拟信号仿真一样,ru n