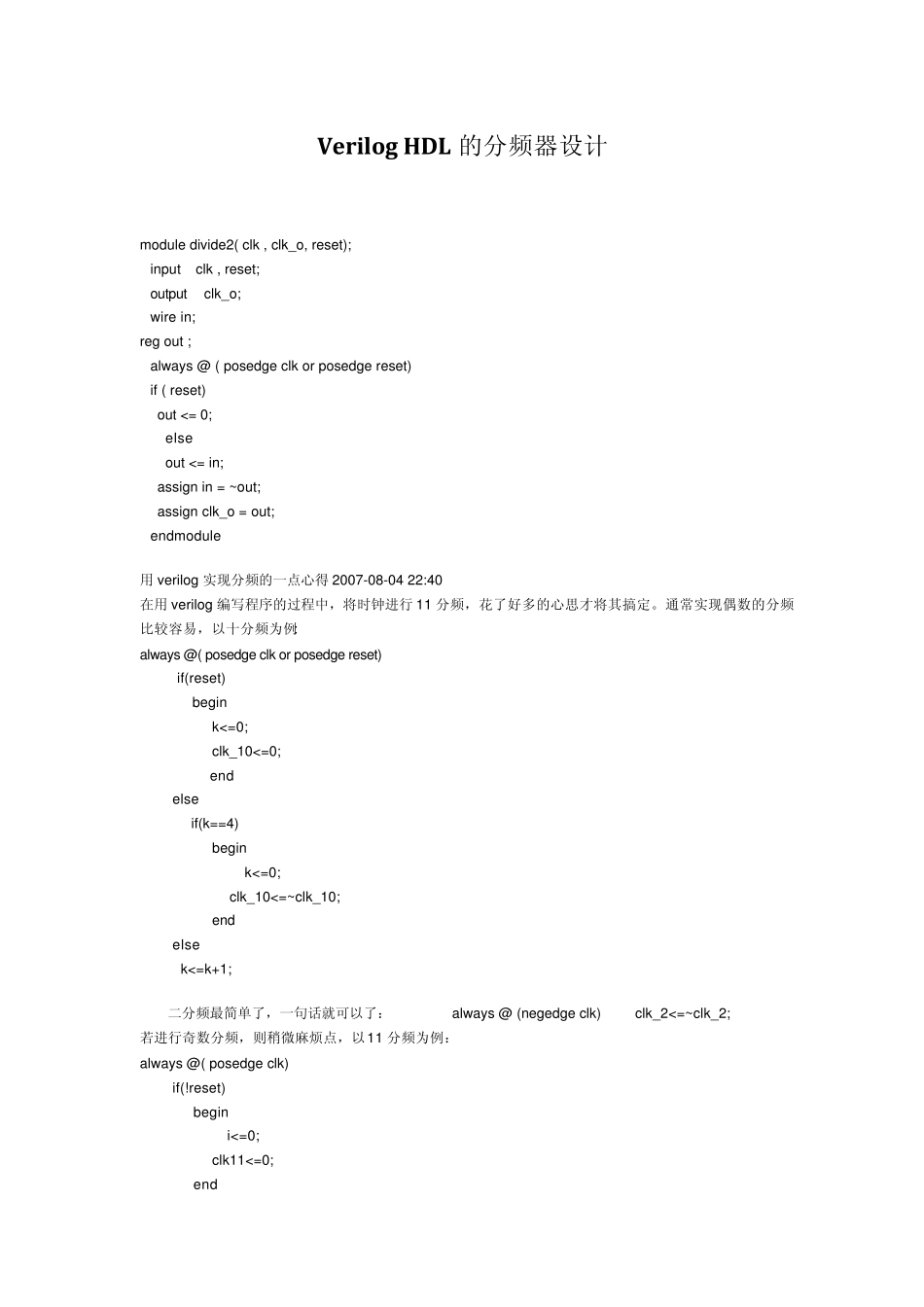

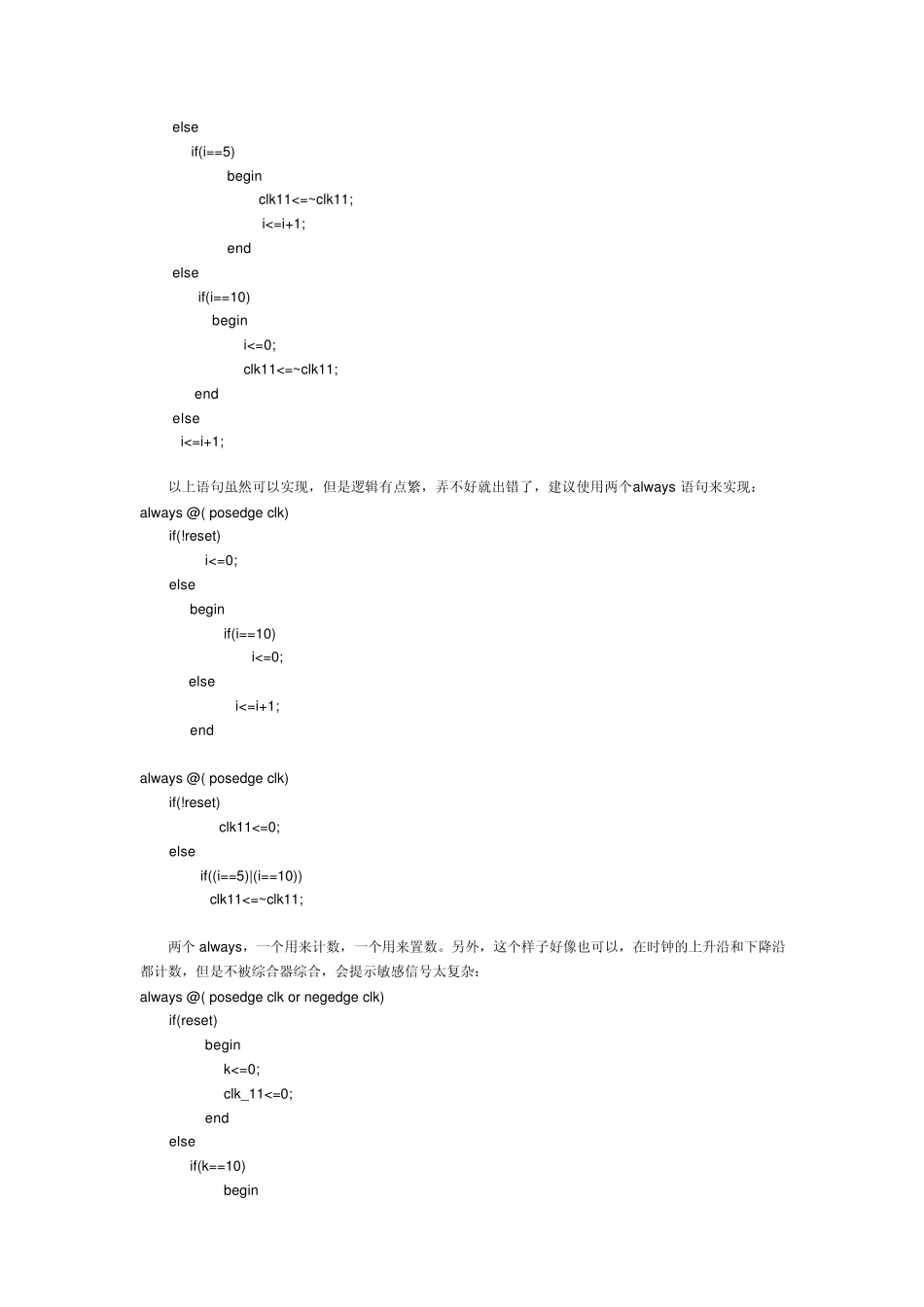

Verilog HDL 的分频器设计 module divide2( clk , clk_o, reset); input clk , reset; output clk_o; wire in; reg out ; always @ ( posedge clk or posedge reset) if ( reset) out <= 0; else out <= in; assign in = ~out; assign clk_o = out; endmodule 用verilog 实现分频的一点心得2007-08-04 22:40 在用verilog 编写程序的过程中,将时钟进行11 分频,花了好多的心思才将其搞定。通常实现偶数的分频比较容易,以十分频为例: always @( posedge clk or posedge reset) if(reset) begin k<=0; clk_10<=0; end else if(k==4) begin k<=0; clk_10<=~clk_10; end else k<=k+1; 二分频最简单了,一句话就可以了: always @ (negedge clk) clk_2<=~clk_2; 若进行奇数分频,则稍微麻烦点,以11 分频为例: always @( posedge clk) if(!reset) begin i<=0; clk11<=0; end else if(i==5) begin clk11<=~ clk11; i<=i+1; end else if(i==10) begin i<=0; clk11<=~ clk11; end else i<=i+1; 以上语句虽然可以实现,但是逻辑有点繁,弄不好就出错了,建议使用两个always 语句来实现: always @( posedge clk) if(!reset) i<=0; else begin if(i==10) i<=0; else i<=i+1; end always @( posedge clk) if(!reset) clk11<=0; else if((i==5)|(i==10)) clk11<=~ clk11; 两个always,一个用来计数,一个用来置数。另外,这个样子好像也可以,在时钟的上升沿和下降沿都计数,但是不被综合器综合,会提示敏感信号太复杂: always @( posedge clk or negedge clk) if(reset) begin k<=0; clk_11<=0; end else if(k==10) begin k<=0; clk_11<=~clk_11; end else k<=k+1; 三分频的Verilog 实现 rickywu 发表于 2005-12-12 11:14:00 //很实用也是笔试面试时常考的,已经经过仿真 占空比要求50%和不要求占空比差别会很大,先看一个占空比50%的描述 module div3(CLKIN,CLKOUT,RESETn); input CLKIN,RESETn; output CLKOUT; //internal counter signals reg[1:0] count_a; reg[1:0] count_b; reg CLKOUT; always @(negedge RESETn or posedge CLKIN) begin if (RESETn==1'b0) count_a<=2'b00; else if (count_a==2'b10) count_a<=2'b00; else count_a<=count_a+1;...