课程设计说明书 1 1、设计目的和要求 1、设计一个 4 位十进制数字频率计

2、测量范围 1~9999Hz,采用 4 位数码管显示,有溢出指示

3、量程有 1KHz,1MHz 两档,用 LED 灯指示

4、读数大于 9999 时,频率计处于超量程状态,发出溢出指示,下次量程,量程自动增大一档

5、读数小时,频率计处于前量程状态,下次测量,量程自动减小一档

6、采用记忆显示方式,在计数与显示电路中间加以锁存电路,每次计数结束,将计数结果送锁存器锁存,并保持到下一个计数结束

2、设计原理 1、基本原理 频率测量的基本原理是计算每秒钟内待测信号的脉冲个数

这就要求 sysclk能产生一个 1s 脉宽的周期信号,并对频率计的每一个计数器 cntp 的使能端进行同步控制

当 clK_cnt 高电平时允许计数,并保持其所计的数

在停止计数期间,首先需要一个锁存信号将计数器在前 1s 的计数值锁存进锁存器 reg 中,并由外部的 7 段译码器译出并稳定显示

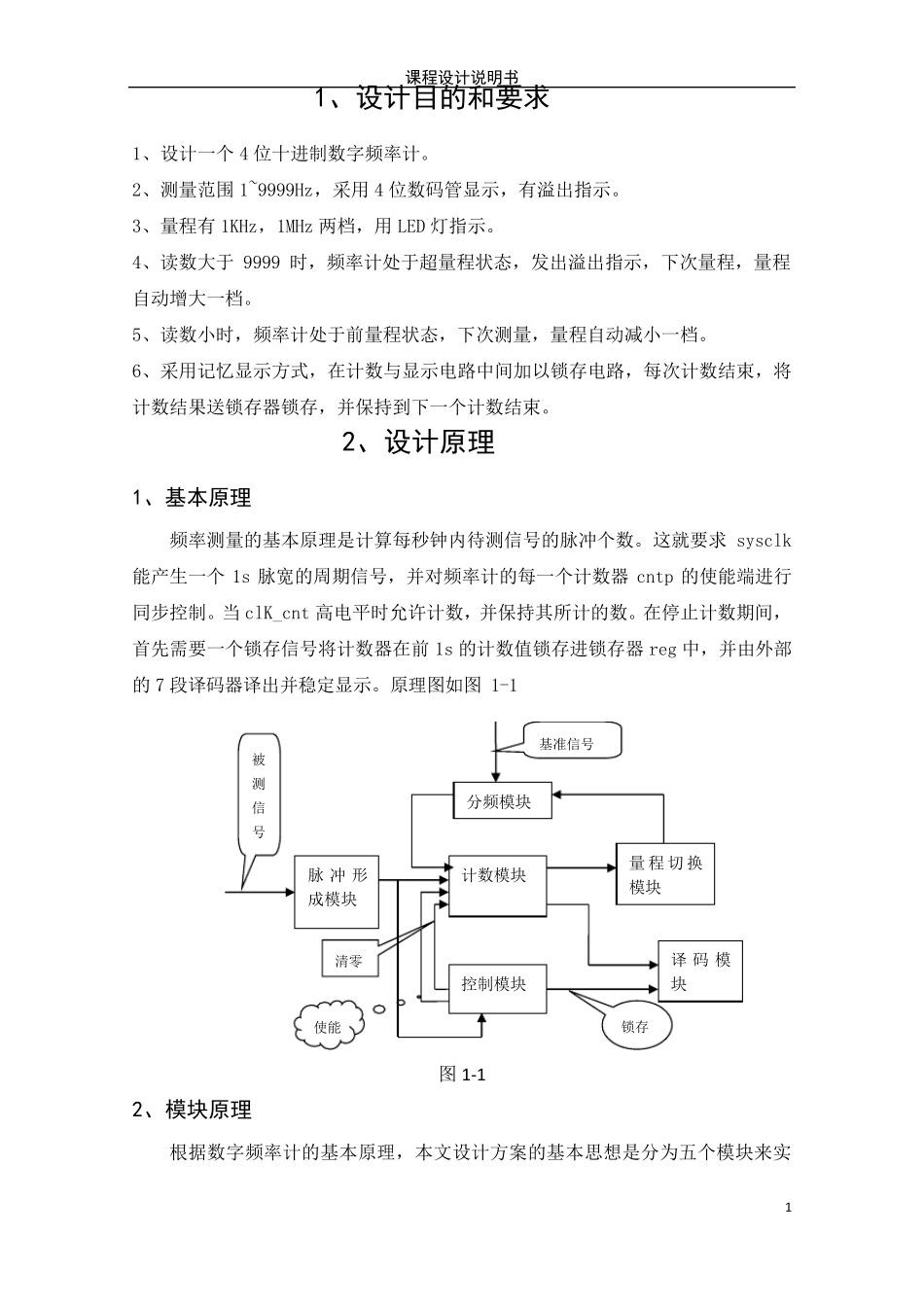

原理图如图 1-1 图 1 -1 2、模块原理 根据数字频率计的基本原理,本文设计方案的基本思想是分为五个模块来实脉 冲 形成模块 计数模块 译 码 模块 控制模块 分频模块 量 程 切 换模块 被测信号 锁存 清零 使能 基准信号 课程设计说明书 2 现其功能,即整个数字频率计系统分为分频模块、控制模块、计数模块、译码模块和量程自动切换模块等几个单元,并且分别用VHDL 对其进行编程,实现了闸门控制信号、计数电路、锁存电路、显示电路等

3、设计内容 1、分频模块 由于晶体振荡器提供的为50MHz 的时钟,而在整个频率计里将用到周期为2s,半个周期为1s 的闸门信号,所以我们在此模块先分频产生0

5Hz 的分频信号

always@(posedge sysclk) begin if(cnt==26’b10_1111_1