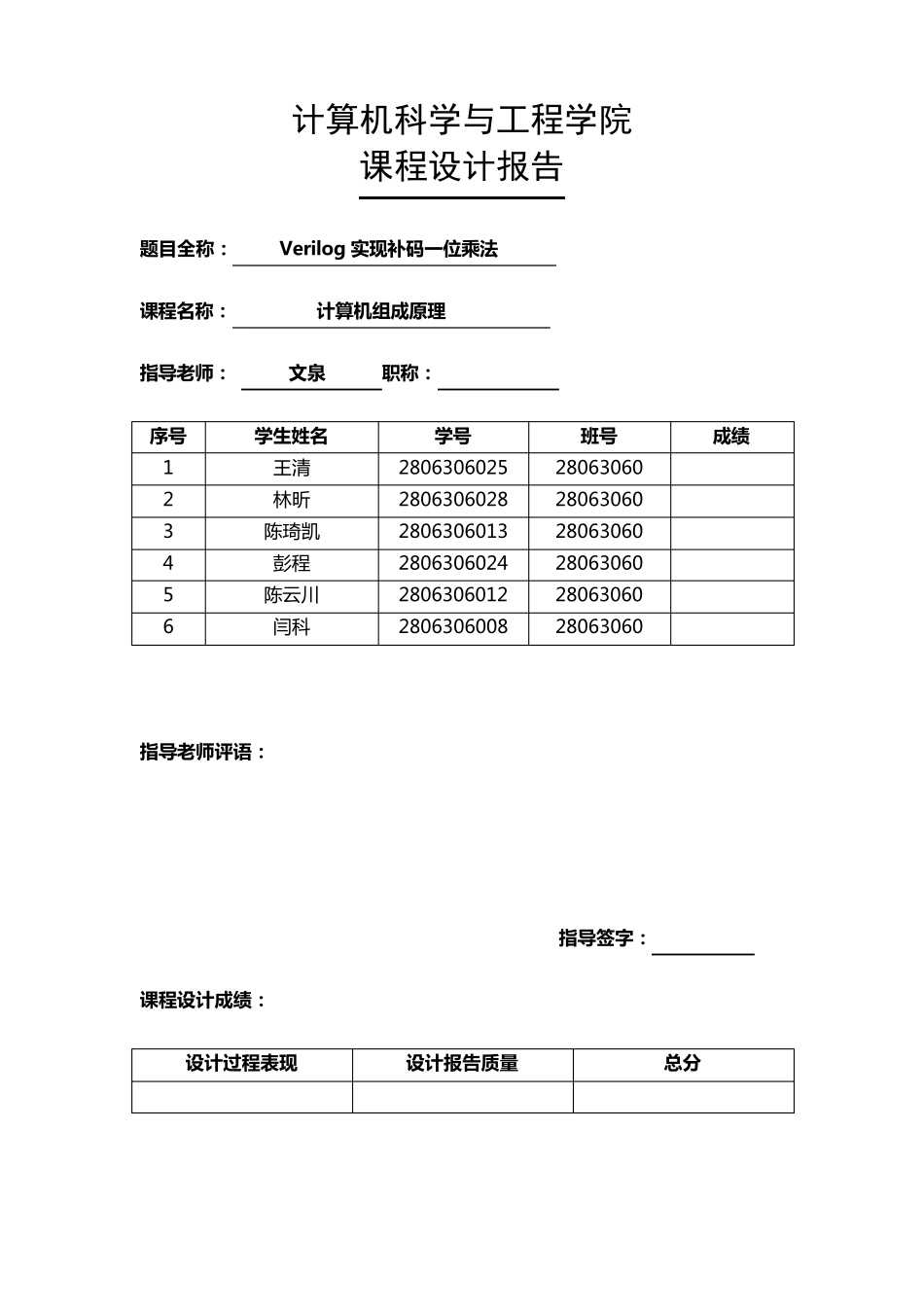

计算机科学与工程学院 课程设计报告 题 目 全 称 : Verilog 实 现 补 码 一位乘法 课程名称 : 计算机组成原理 指导老师: 文泉 职称 : 序号 学生姓名 学号 班号 成绩 1 王 清 2806306025 28063060 2 林 昕 2806306028 28063060 3 陈 琦 凯 2806306013 28063060 4 彭 程 2806306024 28063060 5 陈 云川 2806306012 28063060 6 闫科 2806306008 28063060 指导老师评语: 指导签字: 课程设计成绩: 设计过程表现 设计报告质量 总分 Verilog 实现补码一位乘法设计 目 录 第 1 章 序 言

1 课程设计目的

2 课程设计作用

3 课程设计需求

1 Xilinx 设计软件

2 在 x ilinx ISE 集成开发环境下,使用 Verilog HDL

2 第 2 章 正 文

1 实现补码一位乘法的原理

2 比较补码一位乘法方法