VHDL 仿真,Verilog HDL 仿真入门--ModelSim 使用简介 学硬件描述语言当然得实践,就得用软件仿真

入门其实就是讲下仿真软件怎么用,是很简单的一件事,但是对于刚学的人来说可能有点无从下手

我之前就有点迷茫,所以写这个入门当自己的笔记,也希望能给自学的新手有所帮助

仿真VHDL 和 Verilog HDL 并没有什么区别,一般的软件两种语言也都支持,仿真的步骤和方法也都是一样的

常用的软件有Model Sim 和 Qu artu s II

Qu artu s II 功能很强大

实际的工作经常用它,它提供了功能仿真和时序仿真两种方式,但是作为学习 HDL 并不方便,因为它 compile 编译的时候很慢,对于复杂的逻辑更是要很长时间

好的一点是,Qu artu s II编译后可以清楚的看到它使用了芯片的多少资源,各信号不同的延时等等

另外,Qu artu s II 编译后也可以调用第三方的仿真工具,如 Model Sim 进行仿真

而 Model Sim 只完成逻辑功能的仿真,并不考虑具体使用什么器件,学习 HDL 或者设计逻辑的时候compile一次所用的时间很短,便于调试找出逻辑的错误

所以初学仿真推荐使用Model Sim

本文也只讲下用Model Sim 仿真逻辑的方法

以下部分基本是参照软件帮助简写的,只是原来是英文的而且说的比较繁琐一些,也更详细内容更多

详见 Model Sim 菜单 Help--SE PDF Docu mentation--tu torial

仿真有两种方法

一种是 Basic Simu lation,就是直接建立库,然后编译源文件

另一种是通过建立 Project来仿真,建立 Project 时软件会为它建立一个库,然后的仿真是一样的

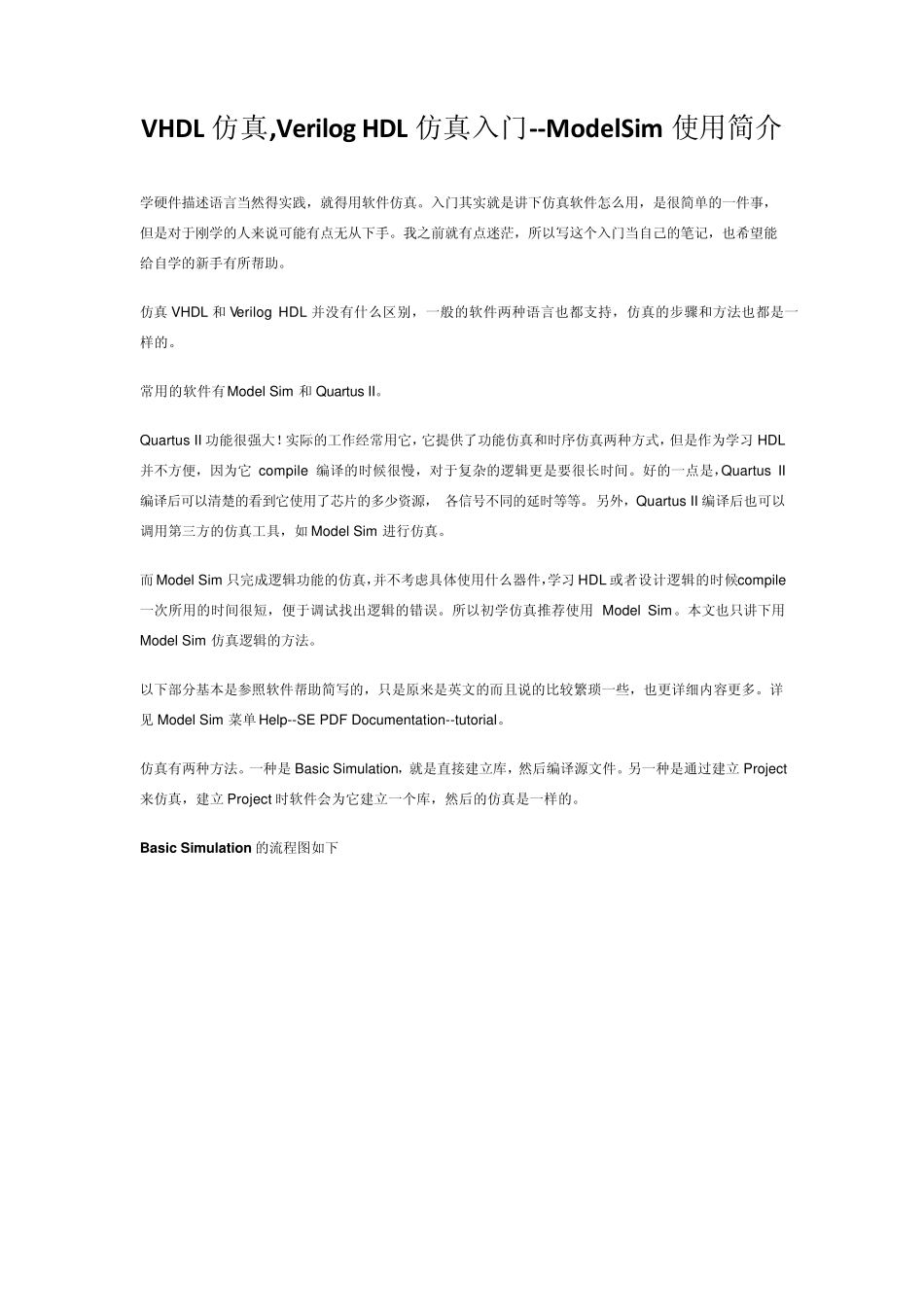

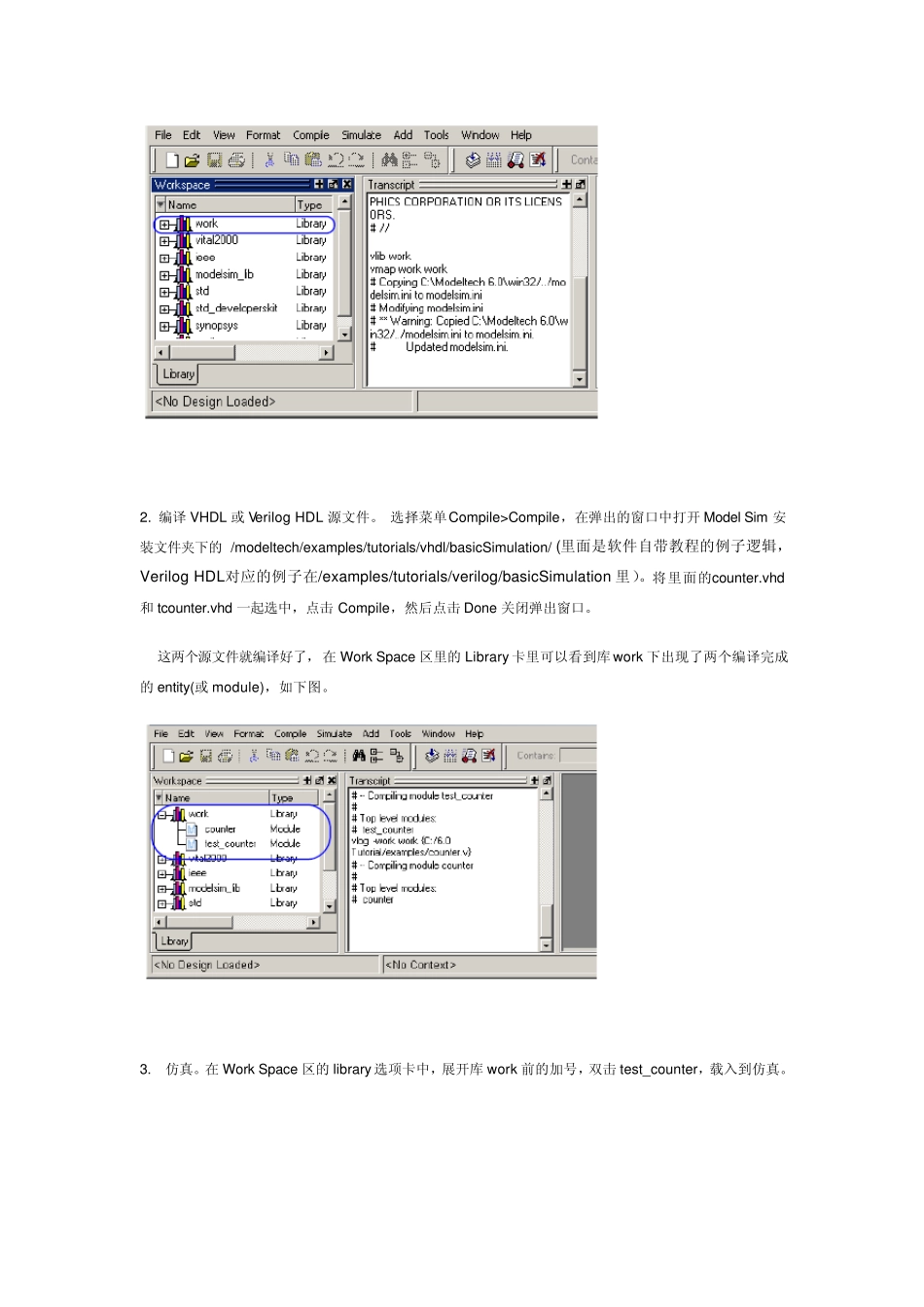

Basic Simu lation 的流程图如下 下面详细写一个例子的步骤