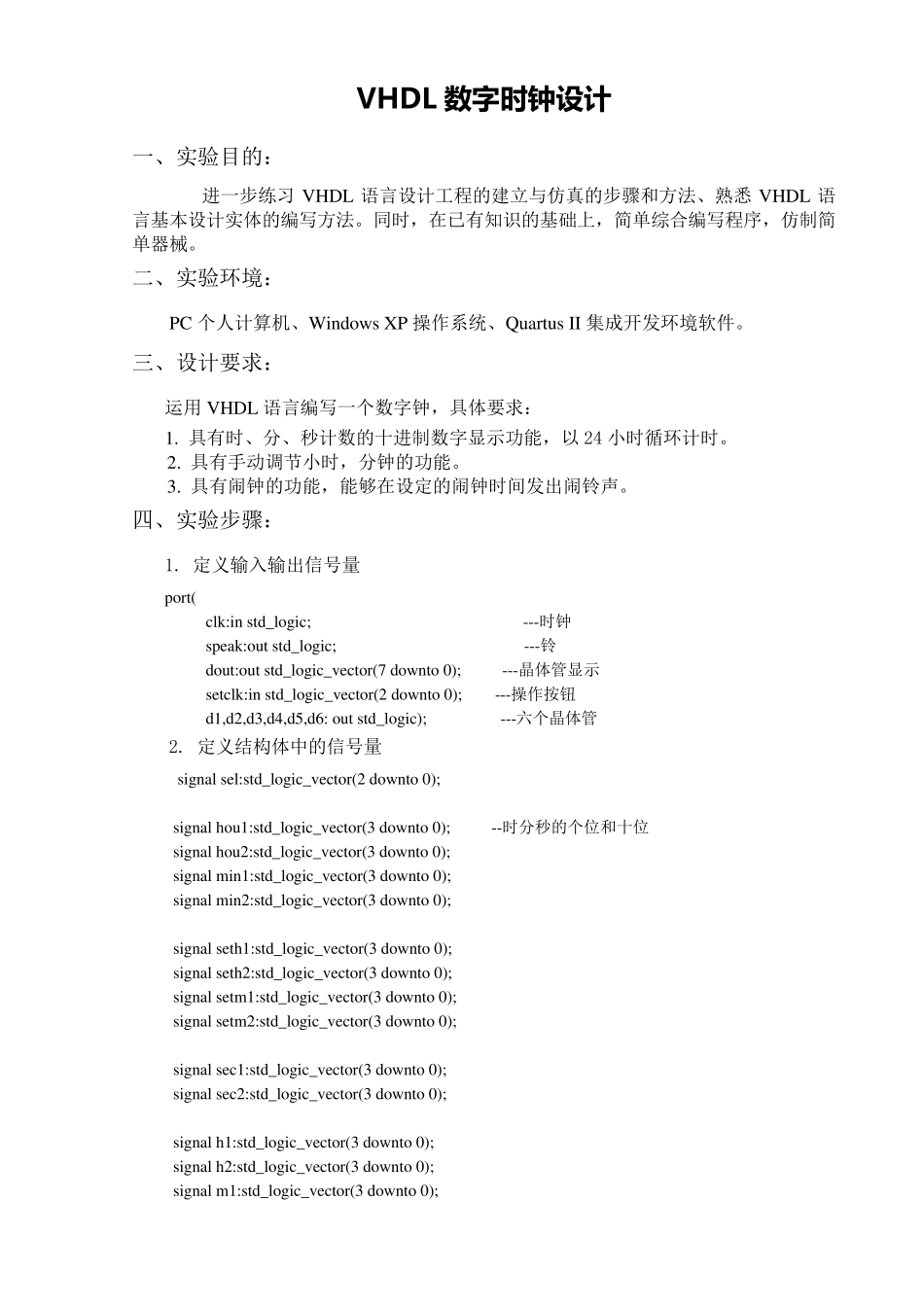

VHDL 数 字时钟设计 一、实验目的: 进一步练习 VHDL 语言设计工程的建立与仿真的步骤和方法、熟悉 VHDL 语言基本设计实体的编写方法

同时,在已有知识的基础上,简单综合编写程序,仿制简单器械

二、实验环境: PC 个人计算机、Window s XP 操作系统、Quartus II 集成开发环境软件

三、设计要求: 运用 VHDL 语言编写一个数字钟,具体要求: 1

具有时、分、秒计数的十进制数字显示功能,以 24 小时循环计时

具有手动调节小时,分钟的功能

具有闹钟的功能,能够在设定的闹钟时间发出闹铃声

四、实验步骤: 1

定义输入输出信号量 port( clk:in std_logic; ---时钟 speak:out std_logic; ---铃 dout:out std_logic_vector(7 dow nto 0); ---晶体管显示 setclk:in std_logic_vector(2 dow nto 0); ---操作按钮 d1,d2,d3,d4,d5,d6: out std_logic); ---六个晶体管 2

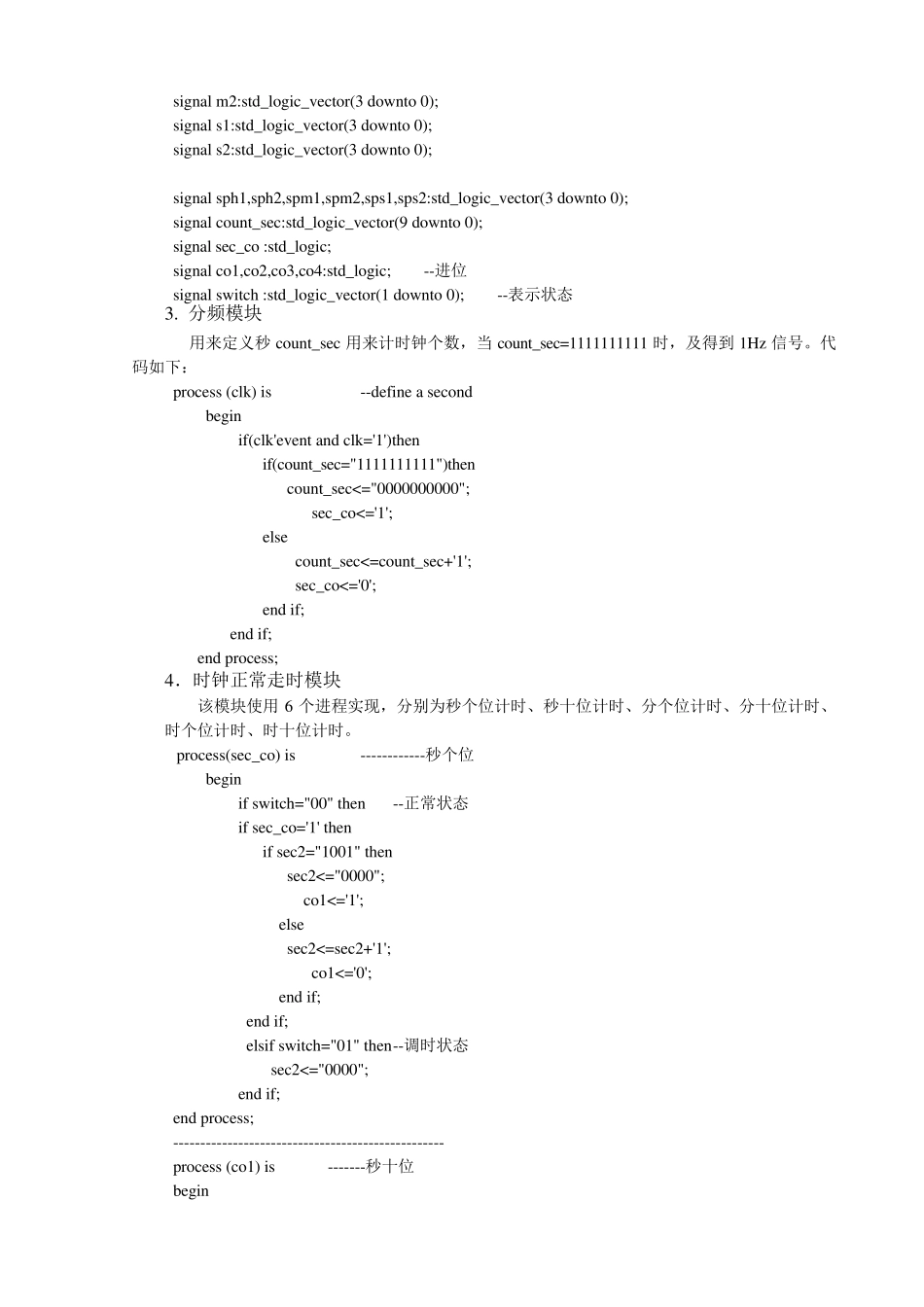

定义结构体中的信号量 signal sel:std_logic_vector(2 dow nto 0); signal hou1:std_logic_vector(3 dow nto 0); --时分秒的个位和十位 signal hou2:std_logic_vector(3 dow nto 0); signal min1:std_logic_vector(3 dow nto 0); signal min2:std_logic_vector(3 dow nto 0); signal seth1:std_logic_vector(3 dow nto 0); signal seth2:std_logic_v