逻辑综合工具Design Compiler 使用教程 编者: 适用专业:电子科学与技术 沈阳理工大学信息学院 2010 年 6 月 图形界面design vision 操作示例 逻辑综合主要是将HDL 语言描述的电路转换为工艺库器件构成的网表的过程

综合工具目前比较主流的是synopsys 公司Design Compiler ,我们在设计实践过程中采用这一工具

Design compiler 有两种工作模式,一种是tcl 模式,另一种为图形模式

在设计中为增强直观性,采用图形界面design vision

TCL 命令行模式可在设计过程中摸索熟悉,并使之成为习惯

tcl 模式在启动工具之前,准备工作有四项:设计的HDL 源文件、采用的工艺库文件、设计的约束文件、工具的启动文件

图形界面模式最少需要前两项,这里不作多说明

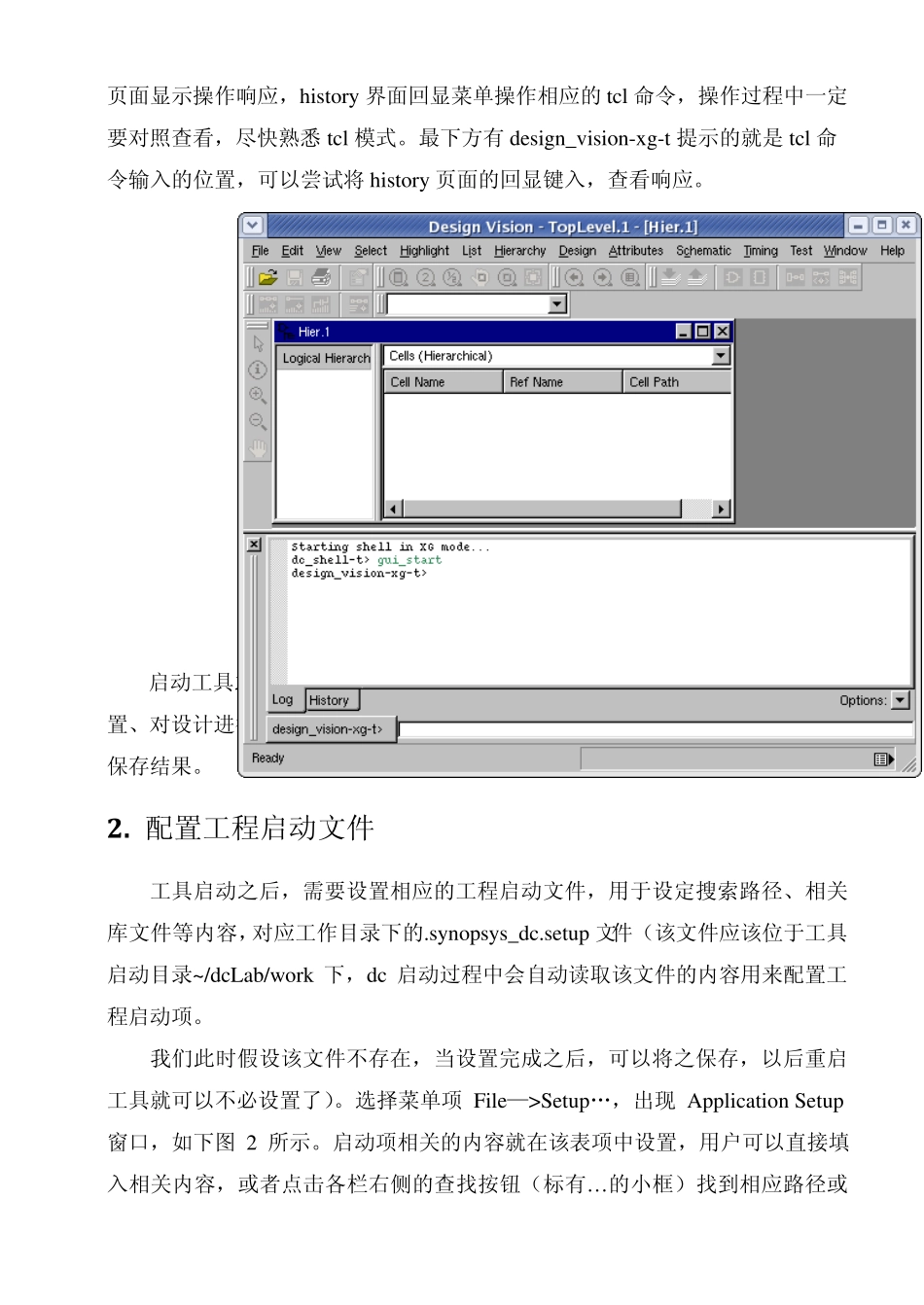

启动工具 登陆 Linux 之后进入的目录即是用户的家目录,在家目录下建立 dcLab 作为本次实验 dc 的操作主目录

在dcLab 目录下,建立设计存放目录如 source、约束文件目录如 constrn、输出网表文件目录 ntlst、报告输出目录 rpt、log 文件目录 log、dc 启动目录 work,等等

实验室中的工作站存放有umc 公司和 tsmc 公司的0

18um 标准单元库的所有文件,存放在目录:/usr/eda/designKit/下面,设计过程中需要查找的话注意路径与示例中的图片上所示路径稍有不同

Design compiler 工具在工作站中已经安装完毕,且用户的环境变量和 license也已设置完成,登录之后直接启动工具即可

如果打开终端之后无法启动工具,可能就是license 没有启动,需要首先采用命令:start_slic 启动license,然后 design vision 才能正常开启与工作

建立相关的工程