实验四 GPS LNA 前仿真实验 实验目的 通过本实验掌握使用在Cadence ADE环境中使用SpectreRF 对LNA 的仿真方法 LNA 介绍 LNA 处在射频接收机的最前端,要求具有最低的噪声系数

LNA 需要具有较高的增益,以抑制后级电路的噪声

LNA 还应具备较高的线性度,降低带外干扰信号对接收机的影响

设计实例:源级电感负反馈LNA 本实验中的LNA 可应用于GPS 接收机,工作频率为1

575GHz左右

(1) LNA 核心电路:ln a2_cell LNA 采用源级电感负反馈结构,(源级负反馈电感由bonding wire 实现),电路图如下

图中,M0 和M1 为两个并联的NMOS 管,作为LNA 的输入管,并联的目的是增加版图中联线的宽度

M3 和M4 是两个并联的NMOS 管,作为共源共栅管,增加LNA 的隔离度

电感L0 和C1 组成谐振网络,是LNA 在1

57GHz处具有较大的增益

M5、M7、R0 和C0 组成LNA 的偏置电路,R0 和C0 用来减小偏置电路的噪声对LNA 噪声系数的影响

电容 C2 作为RF 输入端RFIN 的隔直电容

电容 C4 为输出端的隔直电容

电感L3 和电容 C5 作为输出端的L 型匹配电路

为了防止其它电路的噪声通过地线串扰影响LNA 的噪声系数,在电路中设置了3 种地线:GND1 为主电路的地、GND2 为其它电路的地线,SUB 为所有器件衬底的接地点

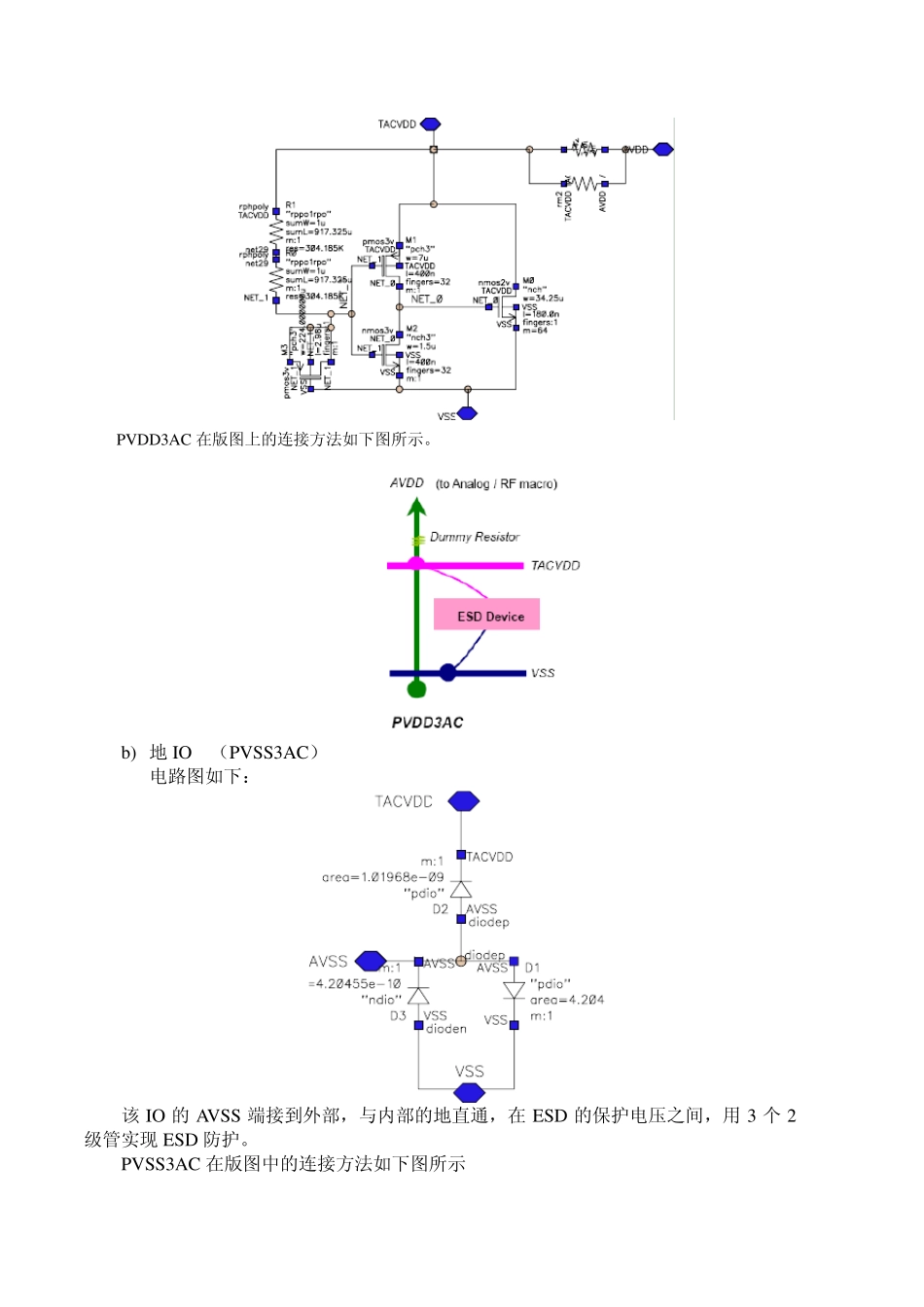

(2) 考虑各接出点的ESD 以后的电路图 ln a2_cell_WPAD 每个 PIN 都需要考虑 ESD,本实验中,我们采用 TSMC 提供的标准 RFIO 作为各PIN 的ESD 器件,LNA 一共有 7 个 IO,所以共有 7 个 ESD 器件

其中LNA 的电源采用电源 ESD 器件(PVDD3AC);SUB 引出采用地线ESD 器件